参数资料

| 型号: | 93C66BT-I/ST |

| 厂商: | Microchip Technology |

| 文件页数: | 6/38页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 4KBIT 2MHZ 8TSSOP |

| 标准包装: | 2,500 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 4K (256 x 16) |

| 速度: | 2MHz |

| 接口: | Microwire 3 线串行 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 8-TSSOP |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

�� �

�

�

�93AA66A/B/C,� 93LC66A/B/C,� 93C66A/B/C�

�2.0�

�FUNCTIONAL� DESCRIPTION�

�2.2�

�Data� In/Data� Out� (DI/DO)�

�When� the� ORG� pin� is� connected� to� V� CC� ,� the� (x16)� orga-�

�nization� is� selected.� When� it� is� connected� to� ground,�

�the� (x8)� organization� is� selected.� Instructions,�

�addresses� and� write� data� are� clocked� into� the� DI� pin� on�

�the� rising� edge� of� the� clock� (CLK).� The� DO� pin� is�

�normally� held� in� a� High-Z� state� except� when� reading�

�data� from� the� device,� or� when� checking� the� Ready/�

�Busy� status� during� a� programming� operation.� The�

�Ready/� Busy� status� can� be� verified� during� an� Erase/�

�Write� operation� by� polling� the� DO� pin;� DO� low� indicates�

�that� programming� is� still� in� progress,� while� DO� high�

�indicates� the� device� is� ready.� DO� will� enter� the� High-Z�

�It� is� possible� to� connect� the� Data� In� and� Data� Out� pins�

�together.� However,� with� this� configuration� it� is� possible�

�for� a� “bus� conflict”� to� occur� during� the� “dummy� zero”�

�that� precedes� the� read� operation,� if� A0� is� a� logic� high�

�level.� Under� such� a� condition� the� voltage� level� seen� at�

�Data� Out� is� undefined� and� will� depend� upon� the� relative�

�impedances� of� Data� Out� and� the� signal� source� driving�

�A0.� The� higher� the� current� sourcing� capability� of� A0,�

�the� higher� the� voltage� at� the� Data� Out� pin.� In� order� to�

�limit� this� current,� a� resistor� should� be� connected�

�between� DI� and� DO.�

�state� on� the� falling� edge� of� CS.�

�2.3�

�Data� Protection�

�2.1�

�Start� Condition�

�All� modes� of� operation� are� inhibited� when� V� CC� is� below�

�a� typical� voltage� of� 1.5V� for� ‘93AA’� and� ‘93LC’� devices�

�The� Start� bit� is� detected� by� the� device� if� CS� and� DI� are�

�both� high� with� respect� to� the� positive� edge� of� CLK� for�

�the� first� time.�

�Before� a� Start� condition� is� detected,� CS,� CLK� and� DI�

�may� change� in� any� combination� (except� to� that� of� a�

�Start� condition),� without� resulting� in� any� device�

�operation� (Read,� Write,� Erase,� EWEN,� EWDS,� ERAL�

�or� WRAL).� As� soon� as� CS� is� high,� the� device� is� no�

�longer� in� Standby� mode.�

�An� instruction� following� a� Start� condition� will� only� be�

�executed� if� the� required� opcode,� address� and� data� bits�

�for� any� particular� instruction� are� clocked� in.�

�or� 3.8V� for� ‘93C’� devices.�

�The� EWEN� and� EWDS� commands� give� additional�

�protection� against� accidentally� programming� during�

�normal� operation.�

�Note:� For� added� protection,� an� EWDS� command�

�should� be� performed� after� every� write�

�operation.�

�After� power-up,� the� device� is� automatically� in� the�

�EWDS� mode.� Therefore,� an� EWEN� instruction� must� be�

�performed� before� the� initial� ERASE� or� WRITE� instruction�

�can� be� executed.�

�Note:�

�When� preparing� to� transmit� an� instruction,�

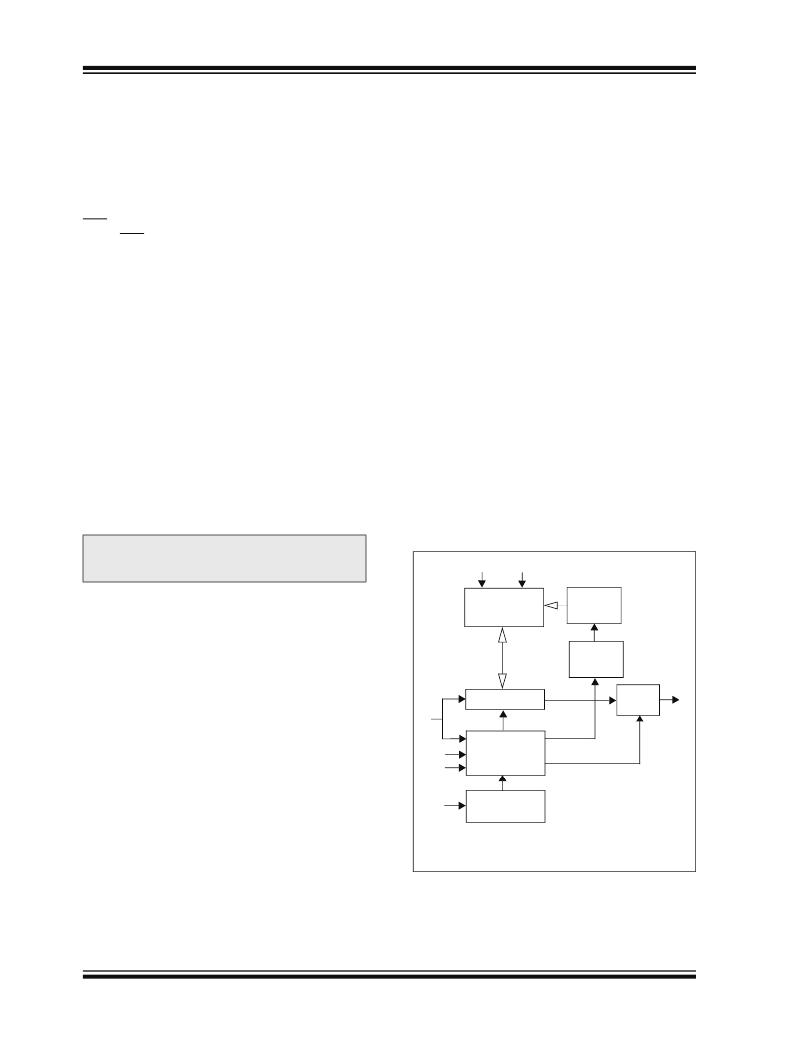

�Block� Diagram�

�either� the� CLK� or� DI� signal� levels� must� be�

�at� a� logic� low� as� CS� is� toggled� active� high.�

�V� CC�

�V� SS�

�Memory�

�Array�

�Address�

�Decoder�

�Address�

�Counter�

�DI�

�ORG*�

�CS�

�CLK�

�Data Register�

�Mode�

�Decode�

�Logic�

�Clock�

�Register�

�Output�

�Buffer�

�DO�

�*ORG� input� is� not� available� on� A/B� devices�

�DS21795E-page� 6�

�?� 2003-2011� Microchip� Technology� Inc.�

�相关PDF资料 |

PDF描述 |

|---|---|

| 93AA66B-I/MS | IC EEPROM 4KBIT 2MHZ 8MSOP |

| 93LC56B-E/SN | IC EEPROM 2KBIT 3MHZ 8SOIC |

| 1658686-3 | CONN D-SUB SOCKET 22-28AWG GOLD |

| ABB95DHLD | CONN EDGECARD 190PS .050 DIP SLD |

| 1658670-3 | CONN PIN 22-28AWG CRIMP GOLD FL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 93C66BTISTG | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4K Microwire Compatible Serial EEPROM |

| 93C66BXEMS | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4K Microwire Compatible Serial EEPROM |

| 93C66BXEMSG | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4K Microwire Compatible Serial EEPROM |

| 93C66BXEOT | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4K Microwire Compatible Serial EEPROM |

| 93C66BXEOTG | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4K Microwire Compatible Serial EEPROM |

发布紧急采购,3分钟左右您将得到回复。