- 您现在的位置:买卖IC网 > PDF目录164926 > 9763-11 (PEREGRINE SEMICONDUCTOR CORP) 3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications PDF资料下载

参数资料

| 型号: | 9763-11 |

| 厂商: | PEREGRINE SEMICONDUCTOR CORP |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | 3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, CQCC68 |

| 封装: | CERAMIC, QFJ-68 |

| 文件页数: | 10/15页 |

| 文件大小: | 351K |

| 代理商: | 9763-11 |

Product Specification

PE9763

Page 4 of 15

2003-2006 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0140-02

│ UltraCMOS RFIC Solutions

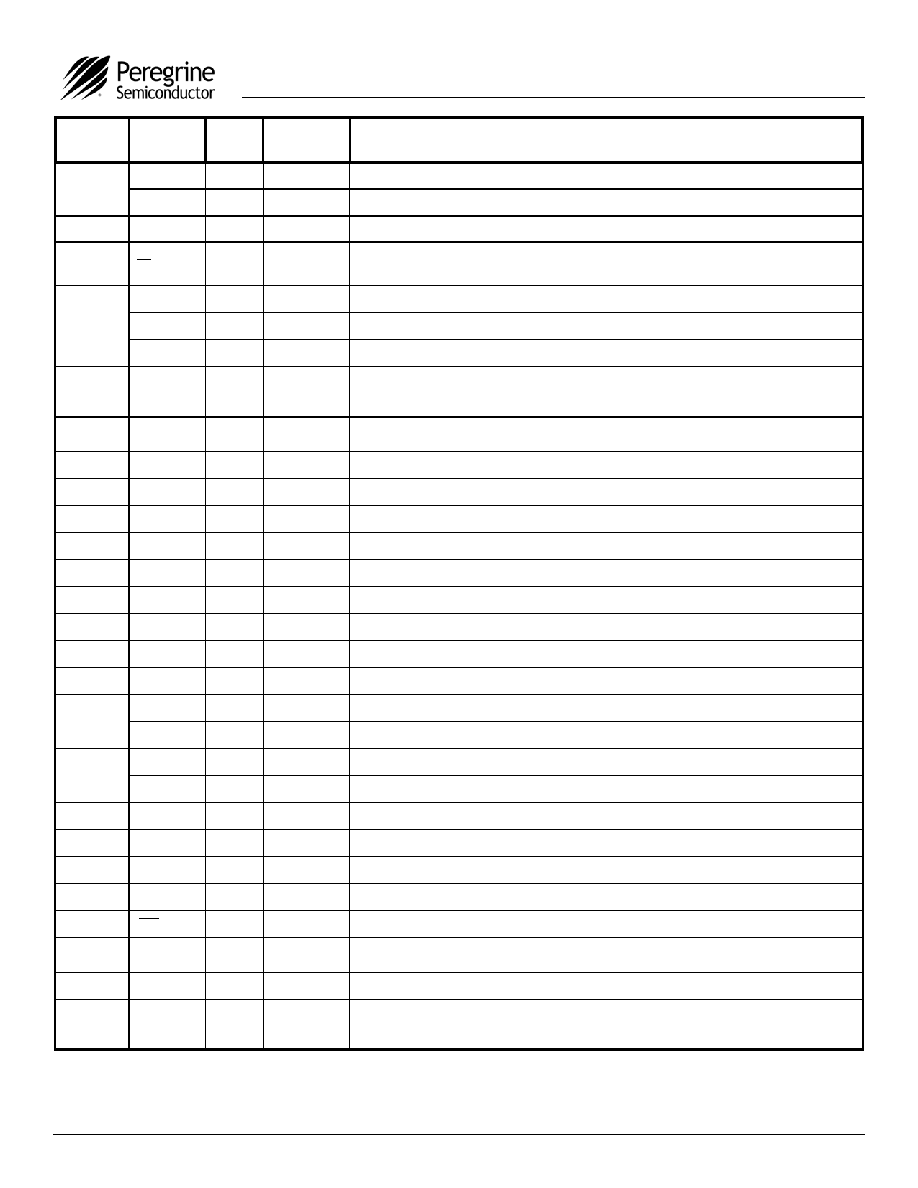

Pin No.

Pin

Name

Valid

Mode

Type

Description

47

Fin

Both

Input

Prescaler input from the VCO. 3.2 GHz max frequency.

48

Fin

Both

Input

Prescaler complementary input. A bypass capacitor should be placed as close as possible to

this pin and be connected in series with a 50

Ω resistor directly to the ground plane.

49

GND

Downbond

Prescaler ground.

GND

Downbond

Prescaler ground.

GND

Downbond

Output driver/charge pump ground.

50

CEXT

Both

Output

Logical “NAND” of PD_

U and PD_D terminated through an on chip, 2 k

Ω series resistor.

Connecting Cext to an external capacitor will low pass filter the input to the inverting amplifier

used for driving LD.

51

LD

Both

Output

Lock detect and open drain logical inversion of CEXT. When the loop is in lock, LD is high

impedance, otherwise LD is a logic low (“0”).

52

DOUT

Both

Output

Data out function, enabled in enhancement mode.

53

VDD

(Note 1)

Output driver/charge pump VDD.

54

GND

Downbond

Output driver/charge pump ground.

55

PD_

D

Both

Output

PD_

D pulses down when f

p leads fc. PD_U is driven to GND when CPSEL = “High”.

56

CP

Both

Output

Charge pump output. Selected when CPSEL = “1”. Tristate when CPSEL = “Low”.

57

PD_

U

Both

Output

PD_

U pulses down when f

c leads fp. PD_D is driven to GND when CPSEL = “High”.

58

GND

Downbond

Output driver/charge pump ground.

59

VDD

(Note 1)

Output driver/charge pump VDD.

GND

Downbond

Phase detector GND.

60

VDD

(Note 1)

Phase detector VDD.

VDD

(Note 1)

ESD VDD.

61

GND

Downbond

ESD ground.

GND

Downbond

Reference ground.

62

fr

Both

Input

Reference frequency input.

63

VDD

(Note 1)

Reference VDD.

64

VDD

(Note 1)

Digital core VDD.

GND

Downbond

Digital core ground.

65

ENH

Both

Input

Enhancement mode. When asserted low (“0”), enhancement register bits are functional.

66

CPSEL

Both

Input

Charge pump select. “High” enables the charge pump and disables pins PD_

U and PD_D by

forcing them “low”. A “low” Tri-states the CP and enables PD_

U and PD_D.

67

MS2_SEL

Both

Input

MASH 1-1 select. “High” selects MASH 1-1 mode. “Low” selects the MASH 1-1-1 mode.

68

RND_SEL

Both

Input

K register LSB toggle enable. “1” enables the toggling of LSB. This is equivalent to having

an additional bit for the LSB of K register. The frequency offset as a result of enabling this bit

is the phase detector comparison frequency / 219.

Note 1:

All VDD pins are connected by diodes and must be supplied with the same positive voltage level.

Note 2:

All digital input pins have 70 k

pull-down resistors to ground.

46

VDD

(Note 1)

ESD VDD.

VDD

(Note 1)

Prescaler VDD.

相关PDF资料 |

PDF描述 |

|---|---|

| 9765-1523-002 | CABLE TERMINATED, MALE, SSMA CONNECTOR, CRIMP, PLUG |

| 98029-0002 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR, SURFACE MOUNT |

| 98029-0003 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR, SURFACE MOUNT |

| 98029-0004 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR, SURFACE MOUNT |

| 98029-0005 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR, SURFACE MOUNT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 97632 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:KUPPLUNG BNC 75 OHM RG59 ROT |

| 97632-00 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| 97632-01 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| 97632-11 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| 97633 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:KUPPLUNG BNC 75 OHM RG59 BLAU |

发布紧急采购,3分钟左右您将得到回复。