- 您现在的位置:买卖IC网 > PDF目录25548 > 97U870AKIT (INTEGRATED DEVICE TECHNOLOGY INC) 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 PDF资料下载

参数资料

| 型号: | 97U870AKIT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 |

| 封装: | MLF-40 |

| 文件页数: | 1/1页 |

| 文件大小: | 281K |

| 代理商: | 97U870AKIT |

Integrated

Circuit

Systems, Inc.

ICS97U87 0

Advance Information

0817—07/07/03

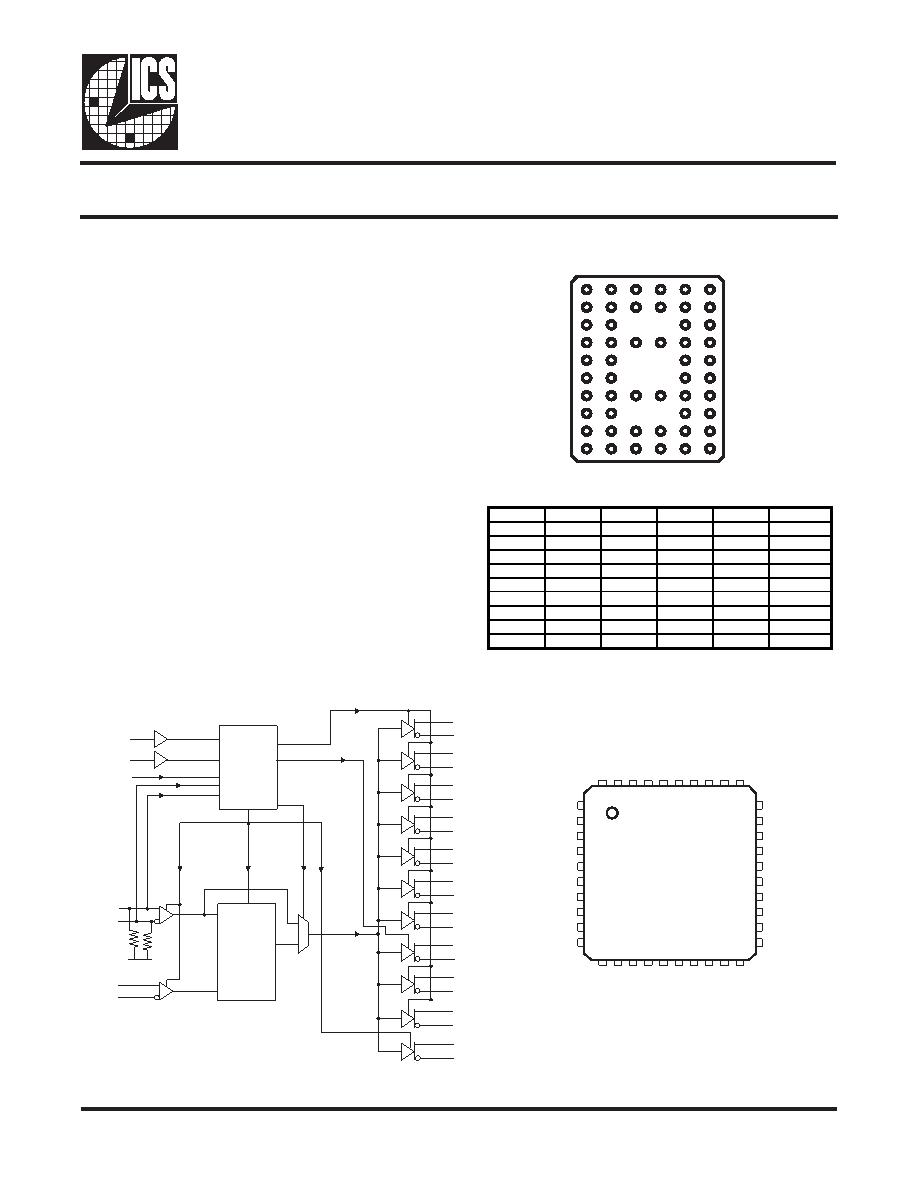

Block Diagram

1.8V Wide Range Frequency Clock Driver

Pin Configuration

40-Pin MLF

Recommended Application:

Custom On-Board Memory / Zero Delay Board Fan Out

Product Description/Features:

ICS Universal Input: Supports multiple switching

standards

Low skew, low jitter PLL clock driver

1 to 10 differential clock distribution (SSTL_18

outputs)

Feedback pins for input to output synchronization

Spread Spectrum tolerant inputs

Switching Characteristics:

Period jitter: 40ps

Half-period jitter: 60ps

CYCLE - CYCLE jitter 40ps

OUTPUT - OUTPUT skew: 40ps

A

B

123456

C

D

E

F

G

H

J

K

52-Ball BGA

ADVANCE INFORMATION documents contain information on products in the formative or design phase development. Characteristic data and other specifications are design goals.

ICS reserves the right to change or discontinue these products without notice. Third party brands and names are the property of their respective owners.

CLKT0

CLKC0

CLKT1

CLKC1

CLKT2

CLKC2

CLKT3

CLKC3

CLKT4

CLKC4

CLKT5

CLKC5

CLKT6

CLKC6

CLKT7

CLKC7

CLKT8

CLKC8

CLKT9

CLKC9

FB_OUTT

FB_OUTC

AV

DD

FB_INT

CLK_INT

CLK_INC

FB_INC

PLL

Powerdown

Control and

Test Logic

OE

LD* or OE

PLL bypass

LD*

LD*, OS or OE

OS

GND

10K-100k

* The Logic Detect (LD) powers down the device when a

logic low is applied to both CLK_INT and CLK_INC.

VDDQ

CLKC2

CLKT2

CLK_INT

CLK_INC

VDDQ

AGND

AVDD

VDDQ

GND

CLKC7

CLKT7

VDDQ

FB_INT

FB_INC

FB_OUTC

FB_OUTT

VDDQ

OE

OS

CLKT3

CLKC3

CLKC4

CLKT4

VDDQ

CLKT9

CLKC9

CLKC8

CLKT8

VDDQ

CLKC1

CLKT1

CLKT0

CLKC0

VDDQ

CLKC5

CLKT5

CLKT6

CLKC6

VDDQ

1

10

11

20

21

31

30

40

ICS97U870

1

234

5

6

A

CLKT1

CLKT0

CLKC0

CLKC5

CLKT5

CLKT6

B

CLKC1

GND

CLKC6

C

CLKC2

GND

NB

GND

CLKC7

D

CLKT2

VDDQ

OS

CLKT7

E

CLK_INT

VDDQ

NB

VDDQ

FB_INT

F

CLK_INC

VDDQ

NB

OE

FB_INC

G

AGND

VDDQ

FB_OUTC

H

AVDD

GND

NB

GND

FB_OUTT

J

CLKT3

GND

CLKT8

K

CLKC3

CLKC4

CLKT4

CLKT9

CLKC9

CLKC8

相关PDF资料 |

PDF描述 |

|---|---|

| 97U870AH | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97U870AHIT | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97U870AKT | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 |

| 97U870AHT | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97U877AHLF-T | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 97U870AKLF | 功能描述:IC CLK DVR PLL 1:10 40VFQFN 制造商:idt, integrated device technology inc 系列:- 包装:托盘 零件状态:有效 类型:驱动器,PLL PLL:带旁路 输入:时钟 输出:SSTL-18 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大值:370MHz 分频器/倍频器:无/无 电压 - 电源:1.7 V ~ 1.9 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:40-VFQFN 裸露焊盘 供应商器件封装:40-VFQFPN(6x6) 标准包装:490 |

| 97U870AKLFT | 功能描述:IC CLK DVR PLL 1:10 40VFQFN 制造商:idt, integrated device technology inc 系列:- 包装:带卷(TR) 零件状态:有效 类型:驱动器,PLL PLL:带旁路 输入:时钟 输出:SSTL-18 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大值:370MHz 分频器/倍频器:无/无 电压 - 电源:1.7 V ~ 1.9 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:40-VFQFN 裸露焊盘 供应商器件封装:40-VFQFPN(6x6) 标准包装:5,000 |

| 97U877AH | 功能描述:时钟驱动器及分配 1.8V DDR-II PLL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| 97U877AHLF | 功能描述:时钟驱动器及分配 1.8V DDR-II PLL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| 97U877AHLFT | 功能描述:时钟驱动器及分配 1.8V DDR-II PLL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。