- 您现在的位置:买卖IC网 > PDF目录25548 > 97ULP877BHLF (INTEGRATED DEVICE TECHNOLOGY INC) 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 PDF资料下载

参数资料

| 型号: | 97ULP877BHLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 封装: | GREEN, PLASTIC, MO-205, MO-225, FBGA-52 |

| 文件页数: | 10/15页 |

| 文件大小: | 252K |

| 代理商: | 97ULP877BHLF |

4

ICS97ULP877B

0981B—03/15/05

Absolute Maximum Ratings

Supply Voltage (VDDQ & AVDD) . . . . . . . . . -0.5V to 2.5V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . GND - 0.5V to VDDQ + 0.5V

Ambient Operating Temperature . . . . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . . . . . -65°C to +150°C

Stresses above those listed under

Absolute Maximum Ratings may cause permanent damage to the device. These

ratings are stress specifications only and functional operation of the device at these or any other conditions above those

listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect product reliability.

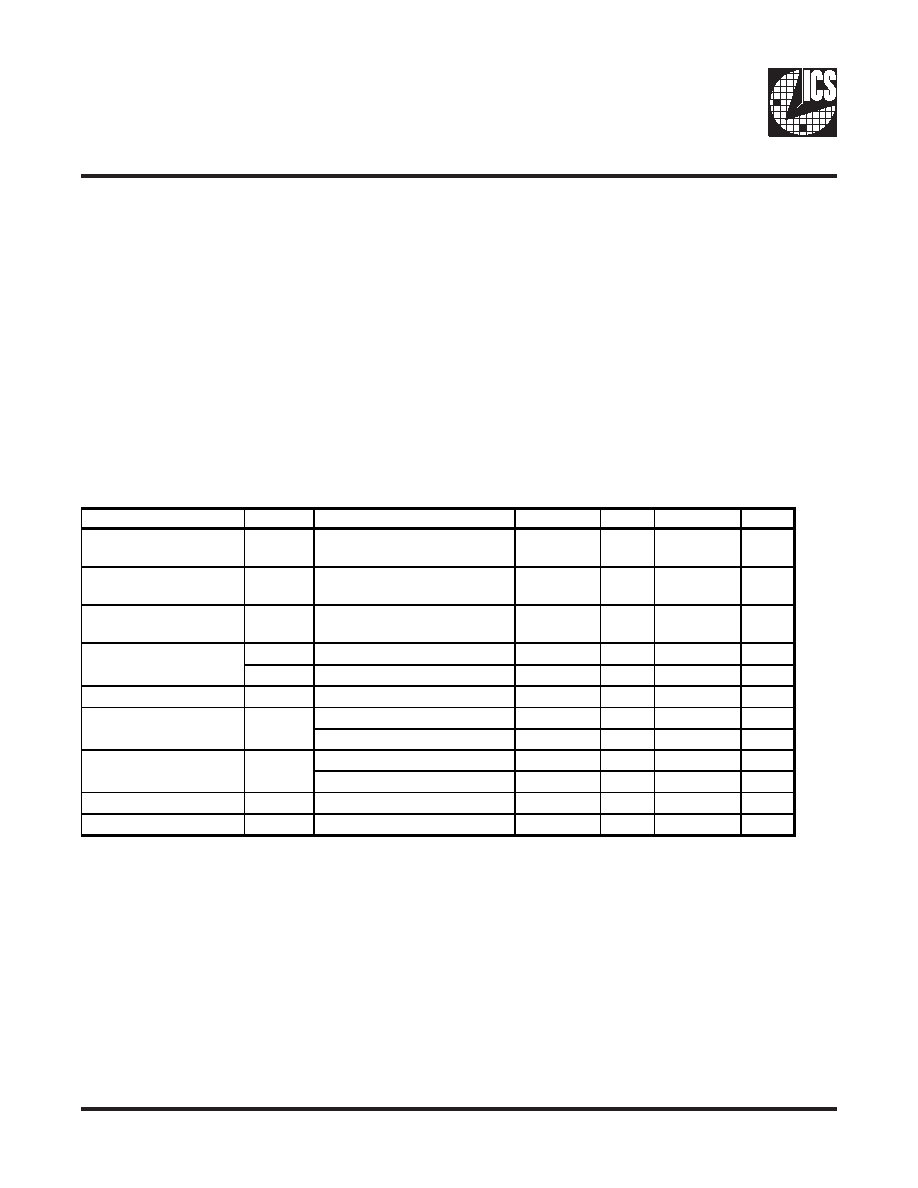

Electrical Characteristics - Input/Supply/Common Output Parameters

TA = 0 - 70°C; Supply Voltage AVDDQ, VDDQ = 1.8 V +/- 0.1V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Input High Current

(CLK_INT, CLK_INC)

IIH

VI = VDDQ or GND

±250

A

Input Low Current (OE,

OS, FB_INT, FB_INC)

IIL

VI = VDDQ or GND

±10

A

Output Disabled Low

Current

IODL

OE = L, VODL = 100mV

100

A

IDD1.8

CL = 0pf @ 270MHz

200

mA

IDDLD

CL = 0pf

500

A

Input Clamp Voltage

VIK

VDDQ = 1.7V Iin = -18mA

-1.2

V

IOH = -100 AVDDQ - 0.2

V

IOH = -9 mA

1.1

1.45

V

IOL=100 A0.25

0.10

V

IOL=9 mA

0.6

V

Input Capacitance

1

CIN

VI = GND or VDDQ

23

pF

Output Capacitance

1

COUT

VOUT = GND or VDDQ

23

pF

1Guaranteed by design, not 100% tested in production.

Operating Supply

Current

High-level output

voltage

VOH

Low-level output voltage

VOL

相关PDF资料 |

PDF描述 |

|---|---|

| 97ULP877BKLF | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| 97ULP877BH | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULPA877AHLF-T | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 980-1 | 0 MHz - 3000 MHz, 140 deg - RF/MICROWAVE COAXIAL MECHANICAL PH SHIFTER |

| 980-2 | 0 MHz - 3000 MHz, 340 deg - RF/MICROWAVE COAXIAL MECHANICAL PH SHIFTER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 97ULP877BHLFT | 功能描述:时钟驱动器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| 97ULP877BKLF/W | 制造商:Integrated Device Technology Inc 功能描述:ZERO DLY PLL CLOCK DRVR SGL 95MHZ TO 410MHZ 40PIN VFQFPN - Tape and Reel |

| 97ULP878AH | 制造商:Integrated Device Technology Inc 功能描述:97ULP878AH - Trays |

| 97ULP878AHLF | 制造商:Integrated Device Technology Inc 功能描述:97ULP878AHLF - Trays |

| 97ULP878AHLFT | 制造商:Integrated Device Technology Inc 功能描述:97ULP878AHLFT - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。