- 您现在的位置:买卖IC网 > PDF目录25564 > 9DB233AGILFT (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 PDF资料下载

参数资料

| 型号: | 9DB233AGILFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 封装: | 4.40 MM, 0.65 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-20 |

| 文件页数: | 8/14页 |

| 文件大小: | 160K |

| 代理商: | 9DB233AGILFT |

IDT

Two Output Differential Buffer for PCIe Gen3

1667C—04/20/11

9DB233

Two Output Differential Buffer for PCIe Gen3

3

Datasheet

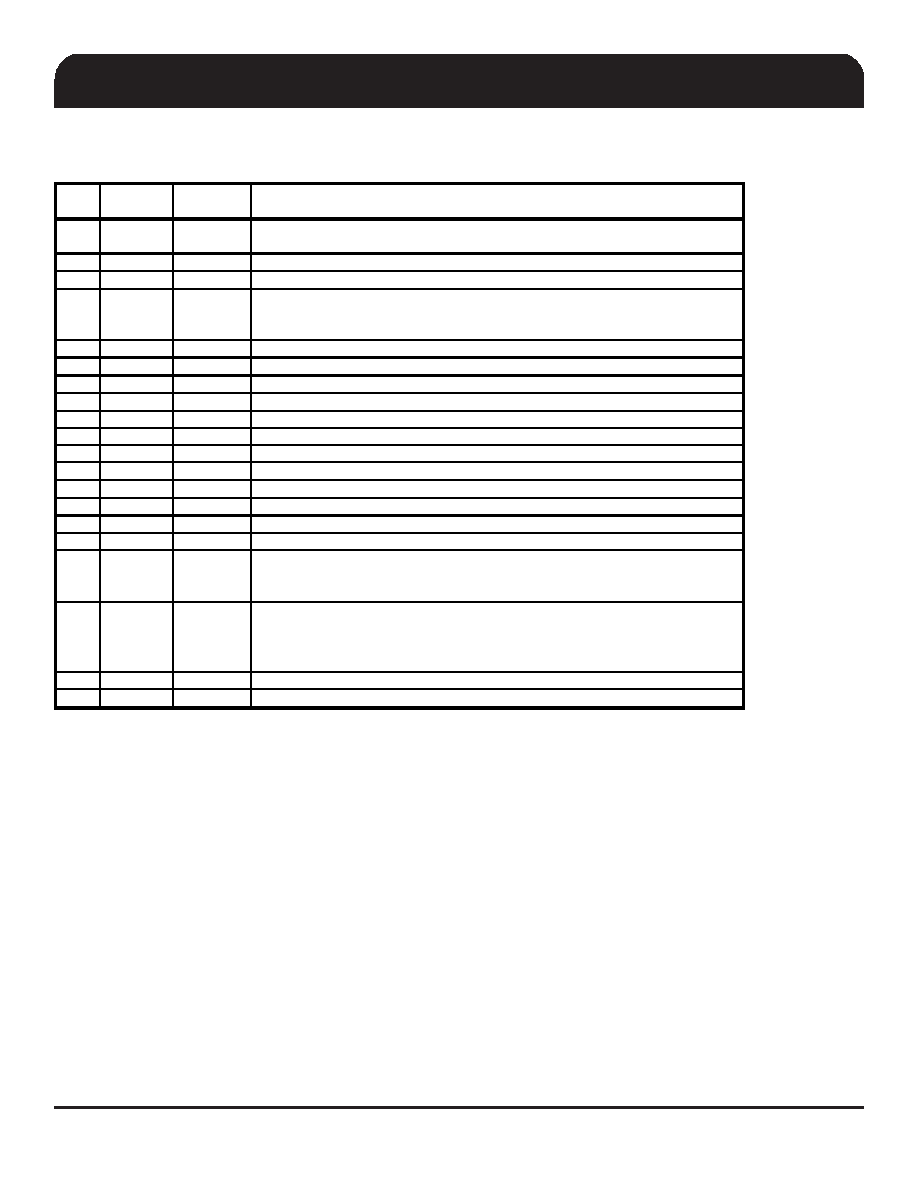

Pin Description

PIN # PIN NAME

PIN TYPE

DESCRIPTION

1PLL_BW

IN

3.3V input for selecting PLL Band Width

0 = low, 1= high

2

SRC_IN

IN

0.7 V Differential SRC TRUE input

3

SRC_IN#

IN

0.7 V Differential SRC COMPLEMENTARY input

4v OE0#

IN

Activ e low input for enabling DIF pair 0. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

5

VDD

PWR

Power supply , nominal 3.3V

6GND

PWR

Ground pin.

7

DIF_0

OUT

0.7V differential true clock output

8

DIF_0#

OUT

0.7V differential Complementary clock output

9

VDD

PWR

Power supply , nominal 3.3V

10

SMBDAT

I/O

Data pin of SMBUS c ircuitry, 5V tolerant

11

SMBCLK

IN

Clock pin of SMBUS c ircuitry, 5V tolerant

12

VDD

PWR

Power supply , nominal 3.3V

13

DIF_1#

OUT

0.7V differential Complementary clock output

14

DIF_1

OUT

0.7V differential true clock output

15

GND

PWR

Ground pin.

16

VDD

PWR

Power supply , nominal 3.3V

17

v OE1#

IN

Activ e low input for enabling DIF pair 1. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

18

IREF

OUT

This pin establishes the reference for the differential current-mode output pairs. It

requires a fixed precision resistor to ground. 475ohm is the standard value for

100ohm differential impedance. Other impedances require different v alues. See

data sheet.

19

GNDA

PWR

Ground pin for the PLL c ore.

20

VDDA

PWR

3.3V power for the PLL core.

Pins preceeded by ' v ' have internal 120K ohm pull down resistors

Note:

相关PDF资料 |

PDF描述 |

|---|---|

| 9DB233AGILF | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 9DB233AGLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 9DB233AFILF | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 9DB233AFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 9DB233AFLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9DB233AGLF | 功能描述:时钟缓冲器 2 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB233AGLFT | 功能描述:时钟缓冲器 2 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB306BF | 制造商:Integrated Device Technology Inc 功能描述:9DB306BF - Rail/Tube |

| 9DB306BFT | 制造商:Integrated Device Technology Inc 功能描述:9DB306BFT - Tape and Reel |

| 9DB306BL | 制造商:Integrated Device Technology Inc 功能描述:PCI EXPRESS, JITTER ATTENUATOR. TSSOP28 - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。