- 您现在的位置:买卖IC网 > PDF目录25564 > 9DB633AFLFT (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF资料下载

参数资料

| 型号: | 9DB633AFLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封装: | 0.209 INCH, ROHS COMPLIANT, MO-150, SSOP-28 |

| 文件页数: | 11/14页 |

| 文件大小: | 182K |

| 代理商: | 9DB633AFLFT |

IDT

Six Output Differential Buffer for PCIe Gen3

1668C—04/20/11

9DB633

Six Output Differential Buffer for PCIe Gen3

6

Datasheet

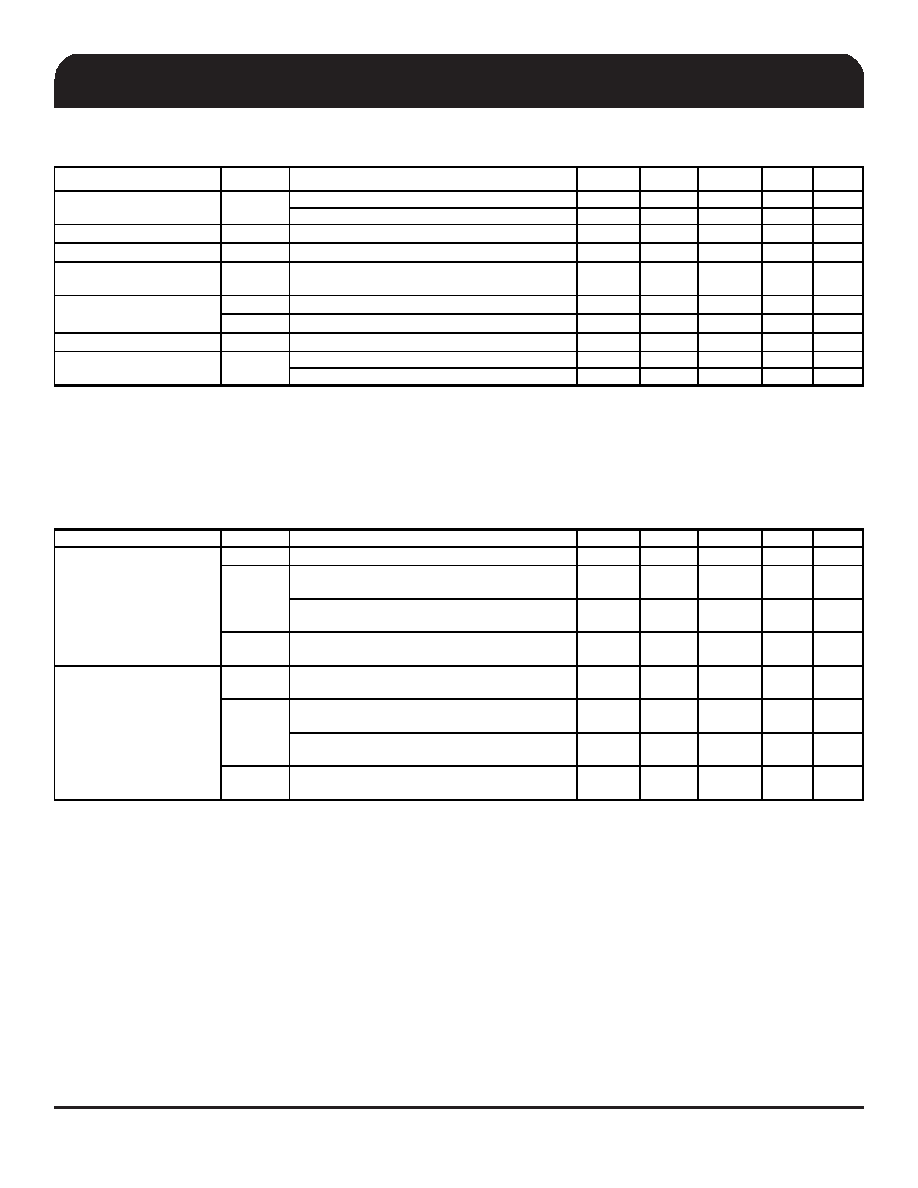

Electrical Characteristics - Output Duty Cycle, Jitter, Skew and PLL Characterisitics

TA = TCOM or TIND; Supply Voltage VDD = 3.3 V +/-5%

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

-3dB point in High BW Mode

2

2.3

4

MHz

1

-3dB point in Low BW Mode

0.4

0.5

1

MHz

1

PLL Jitter Peaking

tJPEAK

Peak Pass band Gain

1

2

dB

1

Duty Cycle

tDC

Measured differentially, PLL Mode

45

48

55

%

1

Duty Cycle Distortion

tDCD

Measured differentially, Bypass Mode @100MHz

-2

1

2

%

1,4

tpdBYP

Bypass Mode, VT = 50%

2500

3660

4500

ps

1

tpdPLL

Hi BW PLL Mode VT = 50%

-250

0

250

ps

1

Skew, Output to Output

tsk3

VT = 50%

15

50

ps

1

PLL mode

40

50

ps

1,3

Additive Jitter in Bypass Mode

10

50

ps

1,3

1Guaranteed by design and characterization, not 100% tested in production.

2 I

REF = VDD/(3xRR).

For RR = 475 (1%), IREF = 2.32mA. IOH = 6 x IREF and VOH = 0.7V @ ZO=50.

3 Measured from differential waveform

4 Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

Skew, Input to Output

Jitter, Cycle to cycle

tjcyc-cyc

PLL Bandwidth

BW

Electrical Characteristics - PCIe Phase Jitter Parameters

TA = TCOM or TIND; Supply Voltage VDD = 3.3 V +/-5%

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Notes

tjphPCIeG1

PCIe Gen 1

32

86

ps (p-p)

1,2,3

PCIe Gen 2 Lo Band

10kHz < f < 1.5MHz

1.1

3

ps

(rms)

1,2

PCIe Gen 2 High Band

1.5MHz < f < Nyquist (50MHz)

2.3

3.1

ps

(rms)

1,2

tjphPCIeG3

PCIe Gen 3

(PLL BW of 2-4MHz, CDR = 10MHz)

0.5

1

ps

(rms)

1,2,4

tjphPCIeG1

PCIe Gen 1

2

5

ps (p-p)

1,2,3

PCIe Gen 2 Lo Band

10kHz < f < 1.5MHz

0.2

0.3

ps

(rms)

1,2

PCIe Gen 2 High Band

1.5MHz < f < Nyquist (50MHz)

0.8

1

ps

(rms)

1,2

tjphPCIeG3

PCIe Gen 3

(PLL BW of 2-4MHz, CDR = 10MHz)

0.1

0.2

ps

(rms)

1,2,4

1 Applies to all outputs.

3 Sample size of at least 100K cycles. This figures extrapolates to 108ps pk-pk @ 1M cycles for a BER of 1-12.

4 Subject to final radification by PCI SIG.

tjphPCIeG2

2 See http://www.pcisig.com for complete specs

tjphPCIeG2

Phase Jitter, PLL Mode

Additive Phase Jitter,

Bypass Mode

相关PDF资料 |

PDF描述 |

|---|---|

| 9DB633AGILFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB633AGLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB633AFILF | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB633AGLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB801BFLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9DB633AFLIFT | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Six Output Differential Buffer for PCIe Gen3 |

| 9DB633AGILF | 功能描述:时钟缓冲器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB633AGILFT | 功能描述:时钟缓冲器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB633AGLF | 功能描述:时钟缓冲器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB633AGLFT | 功能描述:时钟缓冲器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。