- 您现在的位置:买卖IC网 > PDF目录25565 > 9DB803DGT (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF资料下载

参数资料

| 型号: | 9DB803DGT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封装: | 6.10 MM, 0.50 MM PITCH, MO-153, TSSOP-48 |

| 文件页数: | 21/21页 |

| 文件大小: | 249K |

| 代理商: | 9DB803DGT |

IDTTM/ICSTM

Eight Output Differential Buffer for PCIe Gen 2

ICS9DB803D

REV G 01/13/09

ICS9DB803D

Eight Output Differential Buffer for PCIe for Gen 2

9

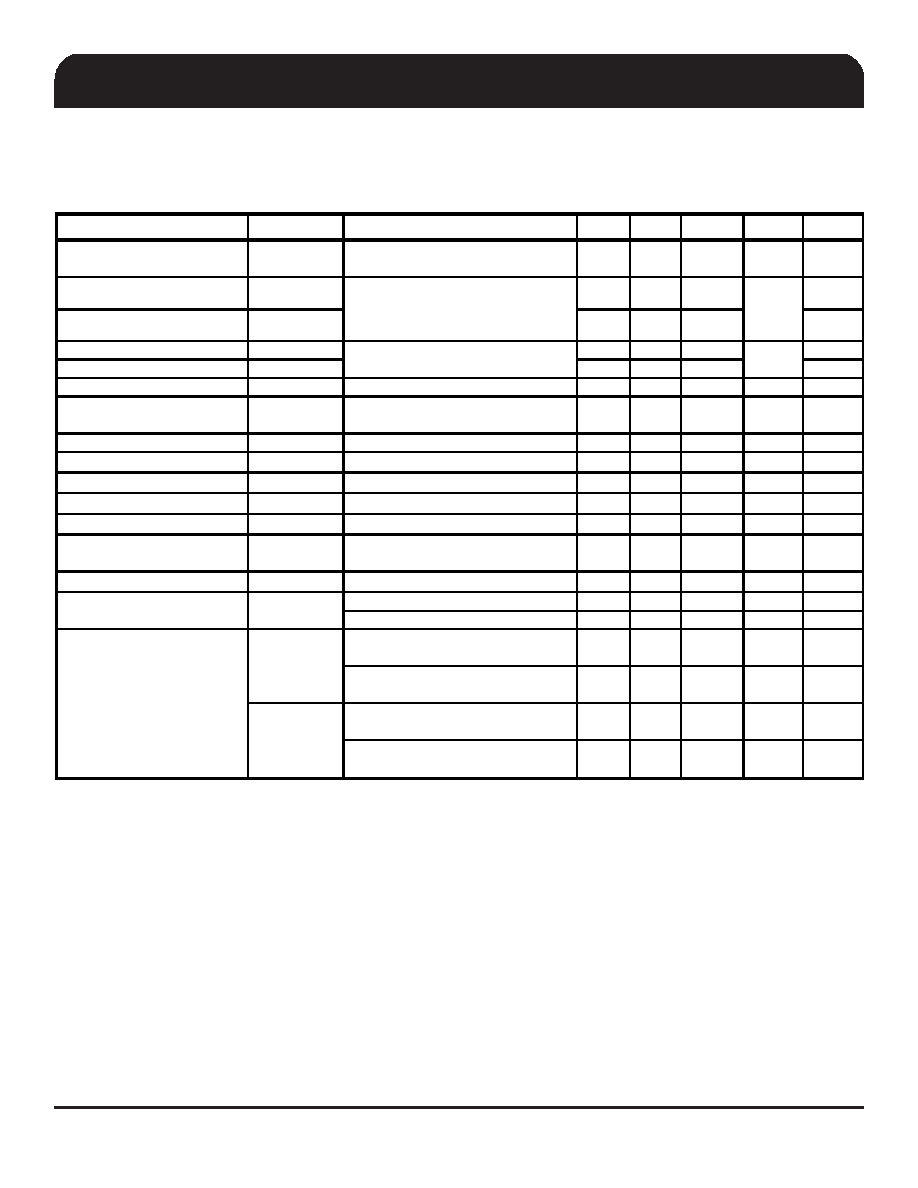

Electrical Characteristics - DIF 0.7V Current Mode Differential Pair

TA = 0 - 70°C; VDD = 3.3 V +/-5%; CL =2pF, RS=33.2, RP=49.9, RREF=475

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

Current Source Output

Impedance

Zo

1

VO = Vx

3000

1

Voltage High

VHigh

660

850

1,3

Voltage Low

VLow

-150

150

1,3

Max Voltage

Vovs

1150

1

Min Voltage

Vuds

-300

1

Crossing Voltage (abs)

Vcross(abs)

250

550

mV

1

Crossing Voltage (var)

d-Vcross

Variation of crossing over all

edges

140

mV

1

Long Accuracy

ppm

see Tperiod min-max values

0

ppm1,2

Rise Time

tr

VOL = 0.175V, VOH = 0.525V

175

700

ps

1

Fall Time

tf

VOH = 0.525V VOL = 0.175V

175

700

ps

1

Rise Time Variation

d-tr

125

ps

1

Fall Time Variation

d-tf

125

ps

1

Duty Cycle

dt3

Measurement from differential

wavefrom

45

50

55

%

1

Skew

tsk3

VT = 50%

50

ps

1

PLL mode

40

50

ps1,5

BYPASS mode as additive jitter

15

50

ps1,5

PCIe Gen 1 specs

(pk to pk value)

30

86

ps

1,6,7

PCIe Gen 2 specs

(rms value)

2.6

3.1

ps

1,6,7

PCIe Gen 1 specs

(pk to pk value)

40

86

ps

1,6,7

PCIe Gen 2 specs

(rms value)

2.8

3.1

ps

1,6,7

1Guaranteed by design and characterization, not 100% tested in production.

3I

REF = VDD/(3xRR). For RR = 475

(1%), I

REF = 2.32mA. IOH = 6 x IREF and VOH = 0.7V @ ZO=50

.

4 Applies to Bypass Mode Only

5 Measured from differential waveform

6 See http://www.pcisig.com for complete specs

7 Device driven by HP81134A Pulse Generator

2 All Long Term Accuracy specifications are guaranteed with the assumption that the input clock complies with

CK409/CK410/CK505 accuracy requirements. The 9DB403/803 itself does not contribute to ppm error.

tjphasePLL

Jitter, Cycle to cycle

tjcyc-cyc

tjphasebypass

Jitter, Phase

Statistical measurement on single

ended signal using oscilloscope

math function.

mV

Measurement on single ended

signal using absolute value.

mV

相关PDF资料 |

PDF描述 |

|---|---|

| 9DB823BFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB823BGLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB833AGILF | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB833AGLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB833AGILFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9DB823BFLF | 功能描述:时钟缓冲器 8 OUTPUT PCIE GEN2 BUFFER w/QPI RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB823BFLFT | 功能描述:时钟缓冲器 8 OUTPUT PCIE GEN2 BUFFER w/QPI RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB823BGLF | 功能描述:时钟缓冲器 8 OUTPUT PCIE GEN2 BUFFER w/QPI RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB823BGLFT | 功能描述:时钟缓冲器 8 OUTPUT PCIE GEN2 BUFFER w/QPI RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB833AFILF | 功能描述:时钟缓冲器 8 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。