- 您现在的位置:买卖IC网 > PDF目录25566 > 9FG108DFILF (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF资料下载

参数资料

| 型号: | 9FG108DFILF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封装: | 0.300 INCH, ROHS COMPLIANT, MO-118, SSOP-48 |

| 文件页数: | 15/18页 |

| 文件大小: | 166K |

| 代理商: | 9FG108DFILF |

IDTTM

Frequency Generator for CPU, QPI, FBD, PCIe Gen 2 & SATA

1542E 12/16/10

ICS9FG108D

Frequency Generator for CPU, QPI, FBD, PCIe Gen 2 & SATA

6

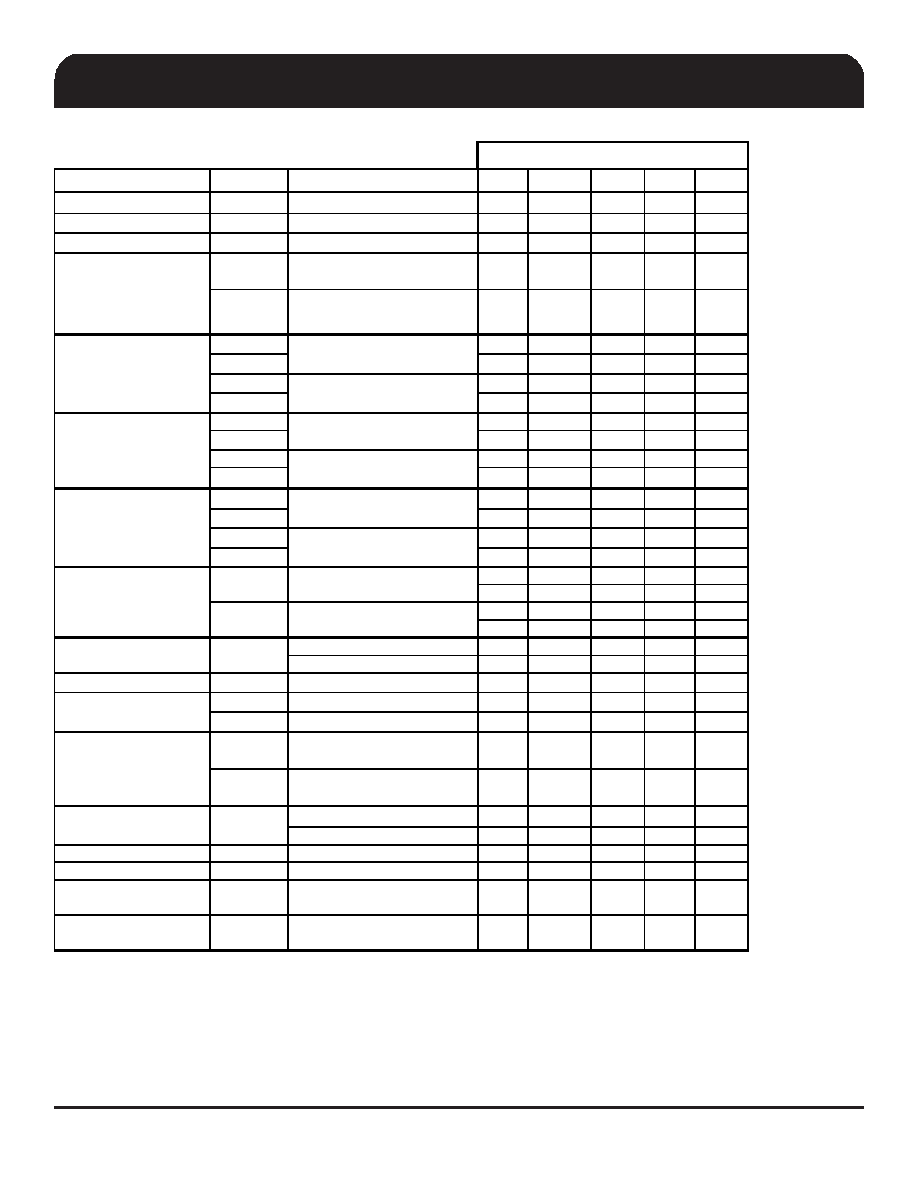

Electrical Characteristics - Input/Supply/Common Output Parameters

TA = Tambient, Supply Voltage VDD = 3.3 V +/-5%

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

Input High Voltage

VIH

3.3 V +/-5%

2

V

DD + 0.3

V1

Input Low Voltage

VIL

3.3 V +/-5%

V

SS - 0.3

0.8

V

1

Input High Current

IIH

VIN = VDD

-5

5

uA

1

IIL1

VIN = 0 V; Inputs with no pull-

up resistors

-5

uA

1

IIL2

VIN = 0 V; Inputs with pull-up

resistors

-200

uA

1

IDDVDD

186

215

mA

1

IDDVDDA

22

25

mA

1

IDDVDD

156

179

mA

1

IDDVDDA

22

25

mA

1

IDDVDDPD

148

170

mA

1

IDDVDDAPD

22

25

mA

1

IDDVDDPD

30

35

mA

1

IDDVDDAPD

22

25

mA

1

IDDVDD

205

236

mA

1

IDDVDD

24

28

mA

1

IDDVDDA

172

198

mA

1

IDDVDDA

24

28

mA

1

163

187

mA

1

24

28

mA

1

33

38

mA

1

24

28

mA

1

SEL14M_25M# = 0

22.50

25.00

28.00

MHz

3

SEL14M_25M# = 1

12.89 14.31818

15.75

MHz

3

Pin Inductance

1

Lpin

7nH

1

CIN

Logic Inputs

1.5

5

pF

1

COUT

Output pin capacitance

6

pF

1

TSTABcom

From VDD Power-Up to 1st

clock

1.8

ms

1,2

TSTABind

From VDD Power-Up to 1st

clock

3ms

1,2

SEL14M_25M# = 0

32.541

kHz

1,3,4

SEL14M_25M# = 1

32.467

kHz

1,3,4

Spread Modulation %

fMOD%DWN

Down Spread Selected

-0.5

%

1,3,4

Spread Modulation %

fMOD%CTR

Center Spread Selected

+/-0.25

%

1,3,4

DIF output enable

tDIFOE

DIF output enable after

DIF_Stop# de-assertion

15

ns

1

Input Rise and Fall times

tR/tF

20% to 80% of VDD

5

ns

1

1Guaranteed by design and characterization, not 100% tested in production.

2See timing diagrams for timing requirements.

All DIF pairs stopped in Hi-Z

mode

3 Input frequency should be measured at the REF pin and tuned to 0 PPM to meet

ppm frequency accuracy on PLL outputs.

4 These values assume 25MHz or 14.31818MHz inputs respectively. Using a higher or lower frequency will scale

these frequencies accordingly. The output frequecy selected by the FS inputs will also scale. For example, 27MHz

input with an FS selection of 100MHz will yield an output frequency of 27/25 x 100 = 108MHz.

All DIF pairs stopped in Hi-Z

mode

CL=Full load; fout = 400 MHz

CL=Full load; fout = 100 MHz

All DIF pairs stopped in driven

mode

Input/Output

Capacitance

1

Fi

Clk Stabilization

1,2

Input Low Current

Operating Supply Current

(TA = Commercial)

DIF_STOP# Current

(TA = Commercial)

Input Frequency

3

CL=Full load; fout = 400 MHz

CL=Full load; fout = 100 MHz

All DIF pairs stopped in driven

mode

IDDVDDPD

IDDVDDAPD

SPEC

Operating Supply Current

(TA = Industrial)

DIF_STOP# Current

(TA = Industrial)

fMOD

Spread Modulation

Frequency

相关PDF资料 |

PDF描述 |

|---|---|

| 9FG108DGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG108DGLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG1200DF-1LFT | 400 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| 9FG1200DG-1LF | 400 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| 9FG1200DF-1LF | 400 MHz, OTHER CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9FG108DFILFT | 功能描述:时钟合成器/抖动清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 9FG108DFLF | 功能描述:时钟合成器/抖动清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 9FG108DFLFT | 功能描述:时钟合成器/抖动清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 9FG108DGILF | 功能描述:时钟合成器/抖动清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 9FG108DGI-LF | 制造商:Integrated Device Technology Inc 功能描述:Programmable PLL Clock Generator Single 48-Pin TSSOP Tube |

发布紧急采购,3分钟左右您将得到回复。