- 您现在的位置:买卖IC网 > PDF目录25570 > 9LPRS535BFLF (INTEGRATED DEVICE TECHNOLOGY INC) SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 PDF资料下载

参数资料

| 型号: | 9LPRS535BFLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 封装: | 0.300 INCH, MO-118, SSOP-48 |

| 文件页数: | 3/17页 |

| 文件大小: | 216K |

| 代理商: | 9LPRS535BFLF |

11

Integrated

Circuit

Systems, Inc.

ICS9LPRS535

Datasheet

1461A—07/28/09

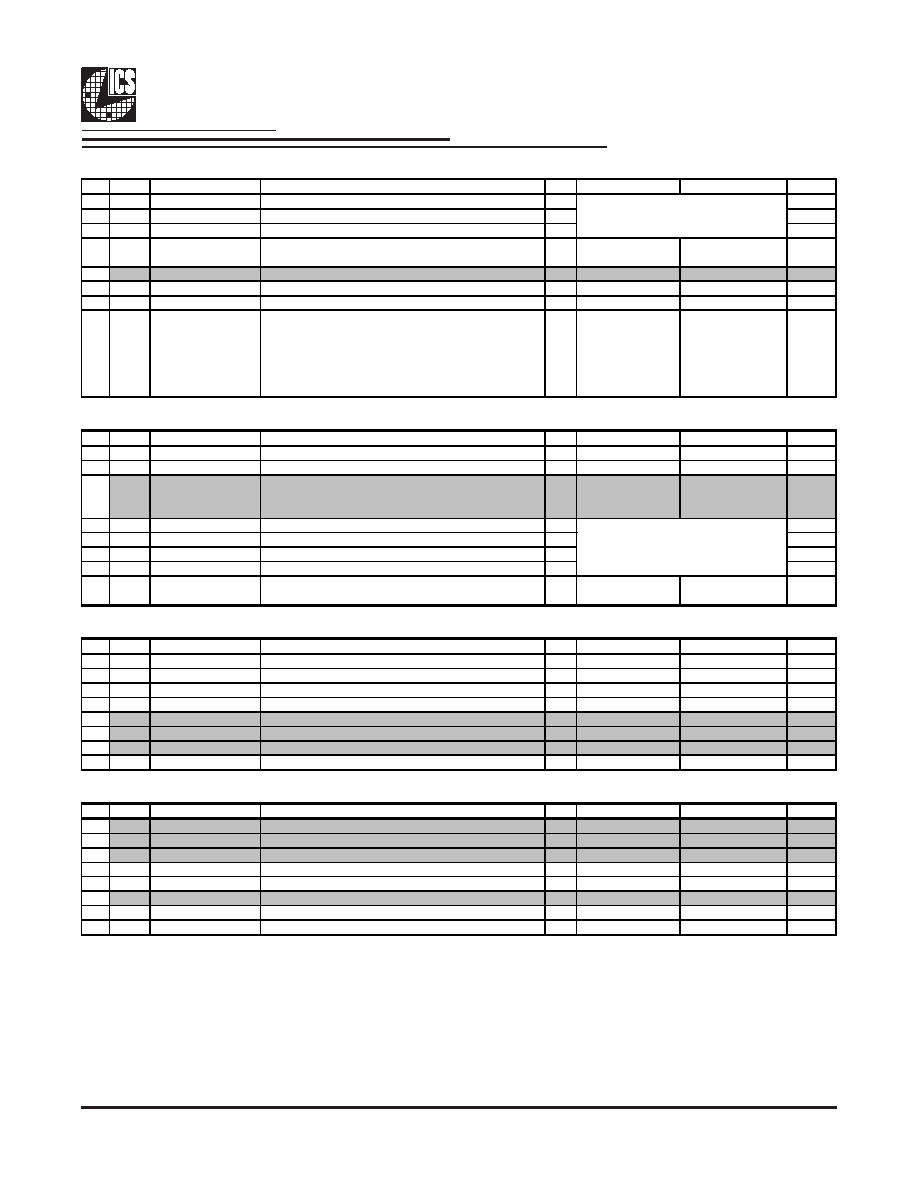

Byte 0 FS Readback and PLL Selection Register

Bit

Pin

Name

Description

Type

0

1

Default

7

-

FSLC

CPU Freq. Sel. Bit (Most Significant)

R

Latch

6

-

FSLB

CPU Freq. Sel. Bit

R

Latch

5

-

FSLA

CPU Freq. Sel. Bit (Least Significant)

R

Latch

4

-

iAMT_EN

Set via SMBus or dynamically by CK505 if detects

dynamic M1

RW

Legacy Mode

iAMT Enabled

0

3

Reserved

RW

0

2

-

SRC_Main_SEL

Select source for SRC Main

R

SRC Main = PLL1

SRC Main = PLL3

0

1

-

SATA_SEL

Select source for SATA clock

RW SATA = SRC_Main

SATA = PLL2

0

-

PD_Restore

1 = on Power Down de-assert return to last known state

0 = clear all SMBus configurations as if cold power-on

and go to latches open state

This bit is ignored and treated at '1' if device is in iAMT

mode.

RW

Configuration Not

Saved

Configuration Saved

1

Byte 1 DOT96 Select and PLL3 Quick Config Register

Bit

Pin

Name

Description

Type

0

1

Default

7

13/14

SRC0_SEL

Select SRC0 or DOT96

RW

SRC0

DOT96

0

6

-

PLL1_SSC_SEL

Select 0.5% down or center SSC

RW

Down spread

Center spread

0

5

Reserved

RW

1

4

PLL3_CF3

PLL3 Quick Config Bit 3

R

1

3

PLL3_CF2

PLL3 Quick Config Bit 2

R

1

2

PLL3_CF1

PLL3 Quick Config Bit 1

R

0

1

PLL3_CF0

PLL3 Quick Config Bit 0

R

0

PCI_SEL

R

PCI from PLL1

PCI from

SRC_MAIN

1

Byte 2 Output Enable Register

Bit

Pin

Name

Description

Type

0

1

Default

7

REF_OE

Output enable for REF, if disabled output is tri-stated

RW

Output Disabled

Output Enabled

1

6

USB_OE

Output enable for USB

RW

Output Disabled

Output Enabled

1

5

PCIF5_OE

Output enable for PCI5

RW

Output Disabled

Output Enabled

1

4

PCI4_OE

Output enable for PCI4

RW

Output Disabled

Output Enabled

1

3

Reserved

RW

1

2

Reserved

RW

1

Reserved

RW

1

0

PCI0_OE

Output enable for PCI0

RW

Output Disabled

Output Enabled

1

Byte 3 Output Enable Register

Bit

Pin

Name

Description

Type

0

1

Default

7

Reserved

RW

1

6

Reserved

RW

1

5

Reserved

RW

1

4

SRC8/ITP_OE

Output enable for SRC8 or ITP

RW

Output Disabled

Output Enabled

1

3

SRC7_OE

Output enable for SRC7

RW

Output Disabled

Output Enabled

1

2

Reserved

RW

1

SRC5_OE

Output enable for SRC5

RW

Output Disabled

Output Enabled

1

0

SRC4_OE

Output enable for SRC4

RW

Output Disabled

Output Enabled

1

25MHz from PLL3 Quick Config

See Table 1 : CPU Frequency Select

Table

相关PDF资料 |

PDF描述 |

|---|---|

| 9LPRS535CFLF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 9LPRS535CGLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 9LPRS545BGLF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 9LPRS545CGLF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 9LPRS545BFLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9LPRS535BFLFT | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 9LPRS535BGLF | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 9LPRS535BGLFT | 制造商:Integrated Device Technology Inc 功能描述:48-PIN CK505 FOR INTEL SYSTEMS 制造商:Integrated Device Technology Inc 功能描述:48 TSSOP (LEAD FREE) - Tape and Reel |

| 9LPRS535CFLF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:48-pin CK505 for Intel Systems |

| 9LPRS535CFLFT | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:48-pin CK505 for Intel Systems |

发布紧急采购,3分钟左右您将得到回复。