- 您现在的位置:买卖IC网 > PDF目录122717 > 9LPRS545CFLFT (INTEGRATED DEVICE TECHNOLOGY INC) SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 PDF资料下载

参数资料

| 型号: | 9LPRS545CFLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 封装: | 0.300 INCH, MO-118, SSOP-48 |

| 文件页数: | 5/17页 |

| 文件大小: | 215K |

| 代理商: | 9LPRS545CFLFT |

13

Integrated

Circuit

Systems, Inc.

ICS9LPRS545

Datasheet

1479A—07/28/09

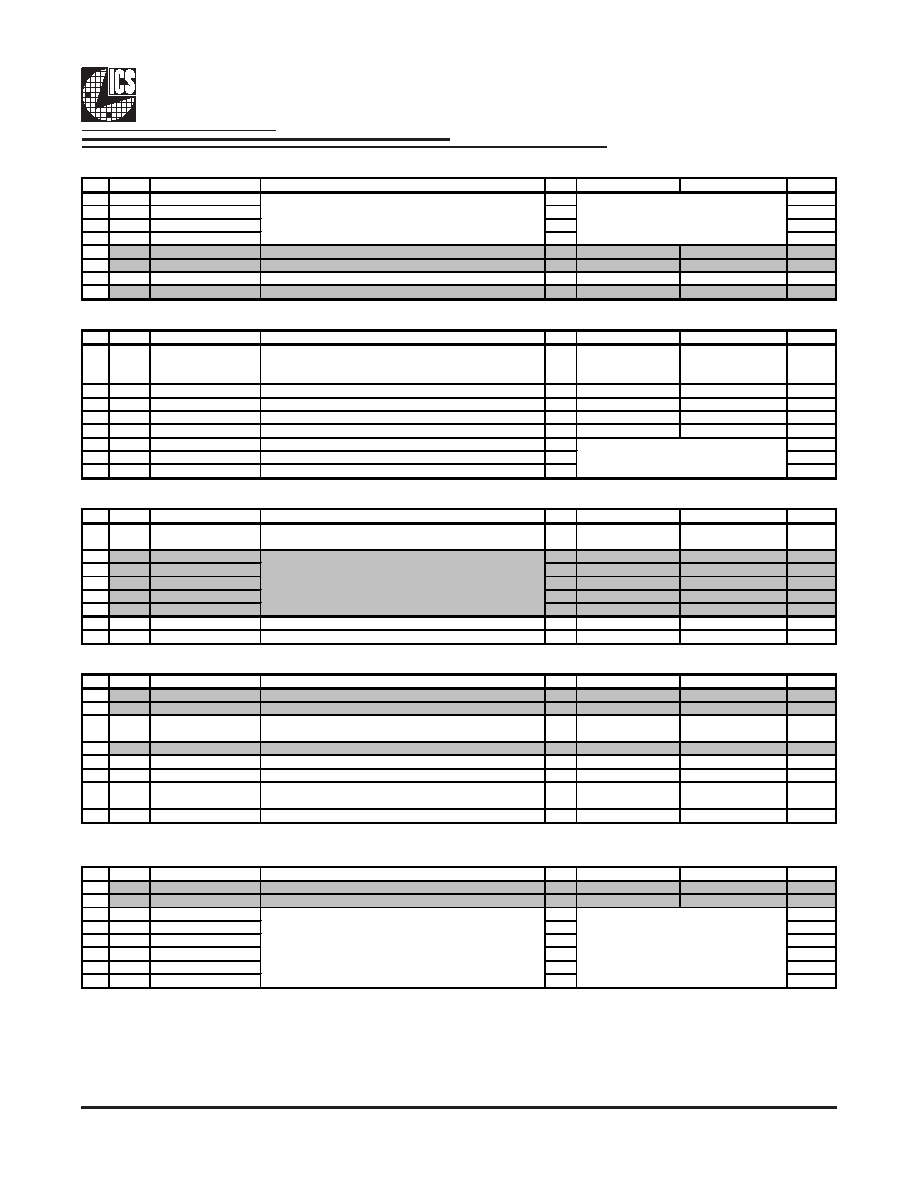

Byte 8 Device ID and Output Enable Register

Bit

Pin

Name

Description

Type

0

1

Default

7

Device_ID3

R

0

6

Device_ID2

R

1

5

Device_ID1

R

1

4

Device_ID0

R

0

3

Reserved

RW

-

0

2

Reserved

RW

-

0

1

SE1_OE

Output enable for SE1

RW

Disabled

Enabled

1

0

Reserved

RW

-

0

Byte 9 Output Control Register

Bit

Pin

Name

Description

Type

0

1

Default

7

PCIF5 STOP EN

Allows control of PCIF5 with assertion of PCI_STOP#

RW

Free running

Stops with

PCI_STOP#

assertion

0

6

TME_Readback

Truested Mode Enable (TME) strap status

R

normal operation

no overclocking

0

5

REF Strength

Sets the REF output drive strength

RW

1X (2Loads)

2X (3 Loads)

1

4

Test Mode Select

Allows test select, ignores REF/FSC/TestSel

RW

Outputs HI-Z

Outputs = REF/N

0

3

Test Mode Entry

Allows entry into test mode, ignores FSB/TestMode

RW

Normal operation

Test mode

0

2

IO_VOUT2

IO Output Voltage Select (Most Significant Bit)

RW

1

IO_VOUT1

IO Output Voltage Select

RW

0

IO_VOUT0

IO Output Voltage Select (Least Significant Bit)

RW

1

Byte 10 Stop Enable Register

Bit

Pin

Name

Description

Type

0

1

Default

7

SRC5_EN Readback

Readback of SRC5 enable latch

R

CPU/PCI Stop

Enabled

SRC5 Enabled

Latch

6

Reserved

RW

TBD

0

5

Reserved

RW

TBD

0

4

Reserved

RW

TBD

0

3

Reserved

RW

TBD

0

2

Reserved

RW

TBD

0

1

CPU 1 Stop Enable

Enables control of CPU1 with CPU_STOP#

RW

Free Running

Stoppable

1

0

CPU 0 Stop Enable

Enables control of CPU 0 with CPU_STOP#

RW

Free Running

Stoppable

1

Byte 11 iAMT Enable Register

Bit

Pin

Name

Description

Type

0

1

Default

7

Reserved

RW

-

0

6

Reserved

RW

-

0

5

WOL_STOP_EN

Enable 25MHz WLAN clock during M1 or Power Down.

This bit is sticky 1.

RW

25MHz disabled in

Powerdown or M1

25MHz enabled in

Powerdown or M1

NOTE

4

Reserved

RW

-

1

3

CPU2_AMT_EN

M1 mode clk enable, only if ITP_EN=1

RW

Disable

Enable

0

2

CPU1_AMT_EN

M1 mode clk enable

RW

Disable

Enable

1

PCI-E_GEN2

Determines if PCI-E Gen2 compliant

R

non-Gen2

PCI-E Gen2

Compliant

1

0

CPU 2 Stop Enable

Enables control of CPU 2 (ITP)with CPU_STOP#

RW

Free Running

Stoppable

1

Note Rev B device default is 0. Rev C device is 1

Byte 12 Byte Count Register

Bit

Pin

Name

Description

Type

0

1

Default

7

Reserved

RW

0

6

Reserved

RW

0

5

BC5

RW

0

4

BC4

RW

0

3

BC3

RW

1

2

BC2

RW

1

BC1

RW

0

BC0

RW

1

Read Back byte count register,

max bytes = 32

Reserved

Table of Device identifier codes, used for

differentiating between CK505 package options, etc.

See Device ID Table

See Table 3: V_IO Selection

(Default is 0.8V)

Byte count is 13 decimal.

相关PDF资料 |

PDF描述 |

|---|---|

| 9173B-01CS08LFT | 75 MHz, VIDEO CLOCK GENERATOR, PDSO8 |

| 951601AFLFT | 66.66 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 954201BFLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 935271490512 | 4 CHANNEL(S), 5M bps, SERIAL COMM CONTROLLER, PQCC68 |

| 935271979118 | 8 I/O, PIA-GENERAL PURPOSE, PQCC16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9LPRS552AGLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS552AGLF GENERAL PURPOSE SEMICONDUCTORS - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS552AGLF General Purpose Semiconductors |

| 9LPRS926EGLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS926EGLF GENERAL PURPOSE SEMICONDUCTORS - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS926EGLF General Purpose Semiconductors |

| 9LPRS926EGLFT | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS926EGLFT LOGIC AND TIMING MISC - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS926EGLFT Logic and Timing Misc |

| 9LQA01241 | 制造商:Denon Electronics 功能描述:REAR PLATE D-M10 |

| 9LQA01441 | 制造商:Denon 功能描述:TOP COVERAVR1600 |

发布紧急采购,3分钟左右您将得到回复。