- 您现在的位置:买卖IC网 > PDF目录294783 > A1415A-2PL84C FPGA, 200 CLBS, 1500 GATES, 200 MHz, PQCC84 PDF资料下载

参数资料

| 型号: | A1415A-2PL84C |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 200 CLBS, 1500 GATES, 200 MHz, PQCC84 |

| 封装: | PLASTIC, MS-007-AE, LCC-84 |

| 文件页数: | 30/68页 |

| 文件大小: | 489K |

| 代理商: | A1415A-2PL84C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

1-210

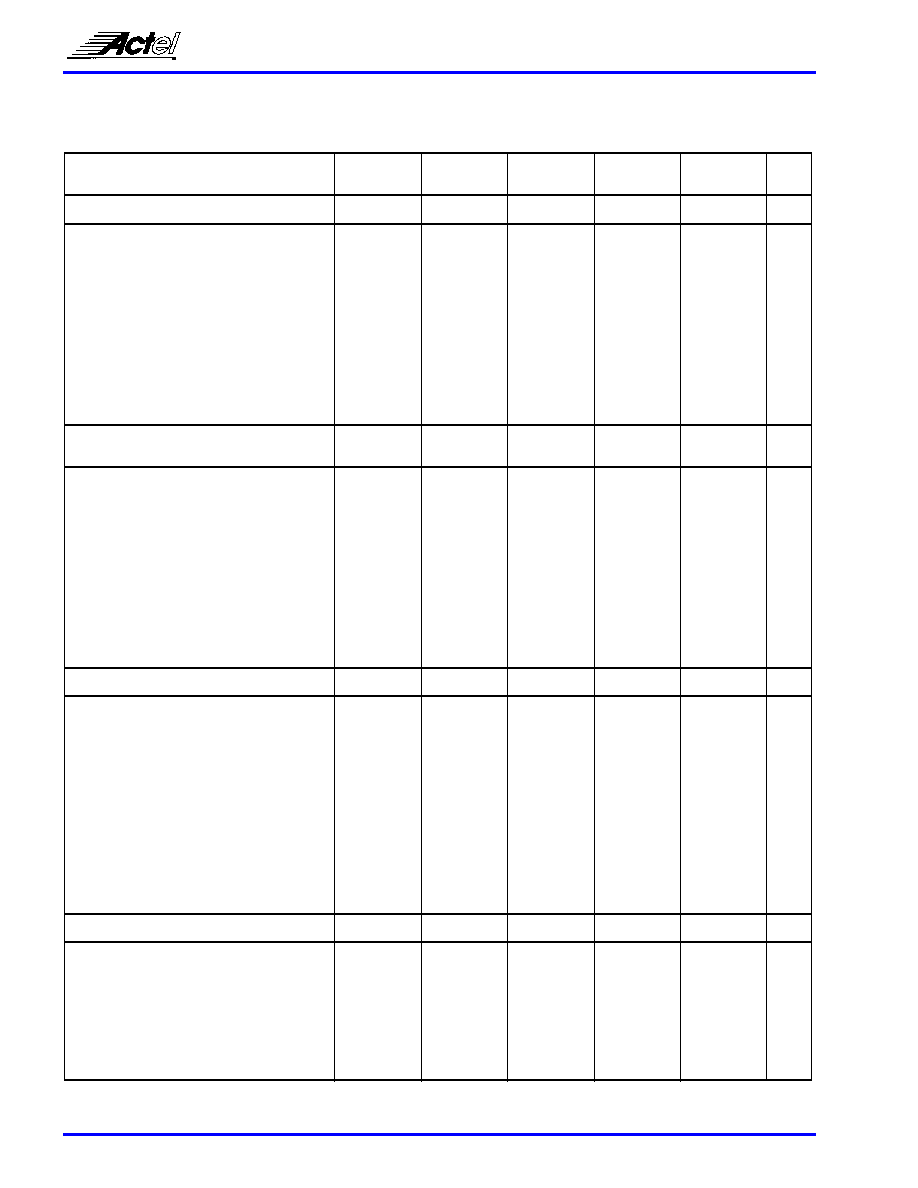

A1440A, A14V40A Timing Characteristics (continued)

(Worst-Case Commercial Conditions)

Note:

1.

Delays based on 35pF loading.

Dedicated (Hard-Wired) I/O Clock

Network

‘–3’ Speed

‘–2’ Speed

‘–1’ Speed

‘Std’ Speed

3.3V Speed

Parameter

Description

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max. Units

tIOCKH

Input Low to High

(Pad to I/O Module Input)

2.0

2.3

2.6

3.0

3.5

ns

tIOPWH

Minimum Pulse Width High

1.9

2.4

3.3

3.8

4.8

ns

tIOPWL

Minimum Pulse Width Low

1.9

2.4

3.3

3.8

4.8

ns

tIOSAPW

Minimum Asynchronous

Pulse Width

1.9

2.4

3.3

3.8

4.8

ns

tIOCKSW

Maximum Skew

0.4

ns

tIOP

Minimum Period

4.0

5.0

6.8

8.0

10.0

ns

fIOMAX

Maximum Frequency

250

200

150

125

100

MHz

Dedicated (Hard-Wired) Array Clock

Network

tHCKH

Input Low to High

(Pad to S-Module Input)

3.0

3.4

3.9

4.5

5.5

ns

tHCKL

Input High to Low

(Pad to S-Module Input)

3.0

3.4

3.9

4.5

5.5

ns

tHPWH

Minimum Pulse Width High

1.9

2.4

3.3

3.8

4.8

ns

tHPWL

Minimum Pulse Width Low

1.9

2.4

3.3

3.8

4.8

ns

tHCKSW

Maximum Skew

0.3

ns

tHP

Minimum Period

4.0

5.0

6.8

8.0

10.0

ns

fHMAX

Maximum Frequency

250

200

150

125

100

MHz

Routed Array Clock Networks

tRCKH

Input Low to High (FO=64)

3.7

4.1

4.7

5.5

9.0

ns

tRCKL

Input High to Low (FO=64)

4.0

4.5

5.1

6.0

9.0

ns

tRPWH

Min. Pulse Width High

(FO=64)

3.3

3.8

4.2

4.9

6.5

ns

tRPWL

Min. Pulse Width Low

(FO=64)

3.3

3.8

4.2

4.9

6.5

ns

tRCKSW

Maximum Skew (FO=128)

0.7

0.8

0.9

1.0

ns

tRP

Minimum Period (FO=64)

6.8

8.0

8.7

10.0

13.4

ns

fRMAX

Maximum Frequency

(FO=64)

150

125

115

100

75

MHz

Clock-to-Clock Skews

tIOHCKSW

I/O Clock to H-Clock Skew

0.0

1.7

0.0

1.8

0.0

2.0

0.0

2.2

0.0

3.0

ns

tIORCKSW

I/O Clock to R-Clock Skew

(FO = 64)

(FO = 144)

0.0

1.0

3.0

0.0

1.0

3.0

0.0

1.0

3.0

0.0

1.0

3.0

0.0

3.0

ns

tHRCKSW

H-Clock to R-Clock Skew

(FO = 64)

(FO = 144)

0.0

1.0

3.0

0.0

1.0

3.0

0.0

1.0

3.0

0.0

1.0

3.0

0.0

1.0

3.0

ns

相关PDF资料 |

PDF描述 |

|---|---|

| A1415A-2PL84I | FPGA, 200 CLBS, 1500 GATES, PQCC84 |

| A1415A-2PLG84C | FPGA, 200 CLBS, 1500 GATES, 200 MHz, PQCC84 |

| A1415A-2PLG84I | FPGA, 200 CLBS, 1500 GATES, PQCC84 |

| A1415A-2PQ100C | FPGA, 200 CLBS, 1500 GATES, 200 MHz, PQFP100 |

| A1415A-2PQ100I | FPGA, 200 CLBS, 1500 GATES, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A1415A-2PL84I | 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 1.5K GATES 200 CELLS 200MHZ 0.8UM 5V 84PLCC - Rail/Tube |

| A1415A-2PLG84C | 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 1.5K GATES 200 CELLS 200MHZ 0.8UM 5V 84PLCC - Rail/Tube |

| A1415A-2PLG84I | 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 1.5K GATES 200 CELLS 200MHZ 0.8UM 5V 84PLCC - Rail/Tube |

| A1415A-2PQ100C | 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 1.5K GATES 200 CELLS 200MHZ 0.8UM 5V 100PQFP - Trays 制造商:Microsemi SOC Products Group 功能描述:FPGA ACT 3 1.5K GATES 200 CELLS 200MHZ 0.8UM 5V 100PQFP - Trays |

| A1415A-2PQ100I | 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 1.5K GATES 200 CELLS 200MHZ 0.8UM 5V 100PQFP - Trays |

发布紧急采购,3分钟左右您将得到回复。