- 您现在的位置:买卖IC网 > PDF目录294785 > A1415A-PLG84I FPGA, 200 CLBS, 1500 GATES, PQCC84 PDF资料下载

参数资料

| 型号: | A1415A-PLG84I |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 200 CLBS, 1500 GATES, PQCC84 |

| 封装: | PLASTIC, MS-007-AE, LCC-84 |

| 文件页数: | 25/68页 |

| 文件大小: | 489K |

| 代理商: | A1415A-PLG84I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

1-205

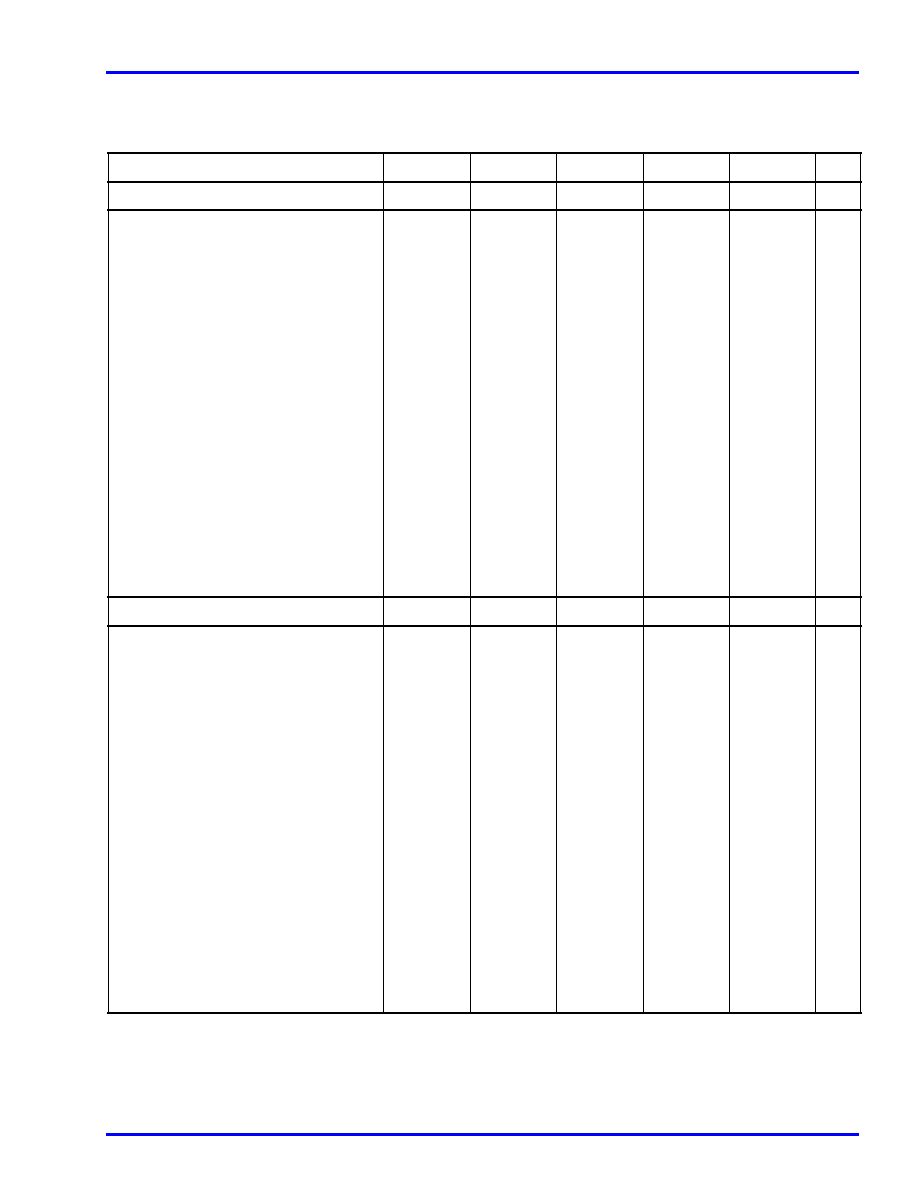

Accelerator Series FPGAs – ACT 3 Family

A1425A, A14V25A Timing Characteristics (continued)

(Worst-Case Commercial Conditions)

Note:

1.

Delays based on 35pF loading.

I/O Module – TTL Output Timing1

‘–3’ Speed

‘–2’ Speed

‘–1’ Speed

‘Std’ Speed

3.3V Speed

Parameter

Description

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max. Units

tDHS

Data to Pad, High Slew

5.0

5.6

6.4

7.5

9.8

ns

tDLS

Data to Pad, Low Slew

8.0

9.0

10.2

12.0

15.6

ns

tENZHS

Enable to Pad, Z to H/L,

Hi Slew

4.0

4.5

5.1

6.0

7.8

ns

tENZLS

Enable to Pad, Z to H/L,

Lo Slew

7.4

8.3

9.4

11.0

14.3

ns

tENHSZ

Enable to Pad, H/L to Z,

Hi Slew

6.5

7.5

8.5

10.0

13.0

ns

tENLSZ

Enable to Pad, H/L to Z,

Lo Slew

6.5

7.5

8.5

10.0

13.0

ns

tCKHS

IOCLK Pad to Pad H/L,

Hi Slew

7.5

9.0

10.0

13.0

ns

tCKLS

IOCLK Pad to Pad H/L,

Lo Slew

11.3

13.5

15.0

19.5

ns

dTLHHS

Delta Low to High, Hi Slew

0.02

0.03

0.04

ns/pF

dTLHLS

Delta Low to High, Lo Slew

0.05

0.06

0.07

0.09

ns/pF

dTHLHS

Delta High to Low, Hi Slew

0.04

0.05

0.07

ns/pF

dTHLLS

Delta High to Low, Lo Slew

0.05

0.06

0.07

0.09

ns/pF

I/O Module – CMOS Output Timing1

tDHS

Data to Pad, High Slew

6.2

7.0

7.9

9.3

12.1

ns

tDLS

Data to Pad, Low Slew

11.7

13.1

14.9

17.5

22.8

ns

tENZHS

Enable to Pad, Z to H/L,

Hi Slew

5.2

5.9

6.6

7.8

10.1

ns

tENZLS

Enable to Pad, Z to H/L,

Lo Slew

8.9

10.0

11.3

13.3

17.3

ns

tENHSZ

Enable to Pad, H/L to Z,

Hi Slew

6.7

7.5

8.5

10.0

13.0

ns

tENLSZ

Enable to Pad, H/L to Z,

Lo Slew

6.7

7.5

9.0

10.0

13.0

ns

tCKHS

IOCLK Pad to Pad H/L,

Hi Slew

8.9

10.7

11.8

15.3

ns

tCKLS

IOCLK Pad to Pad H/L,

Lo Slew

13.0

15.6

17.3

22.5

ns

dTLHHS

Delta Low to High, Hi Slew

0.04

0.05

0.06

0.08

ns/pF

dTLHLS

Delta Low to High, Lo Slew

0.07

0.08

0.09

0.11

0.14

ns/pF

dTHLHS

Delta High to Low, Hi Slew

0.03

0.04

0.05

ns/pF

dTHLLS

Delta High to Low, Lo Slew

0.04

0.05

0.07

ns/pF

相关PDF资料 |

PDF描述 |

|---|---|

| A1415A-PQG100C | FPGA, 200 CLBS, 1500 GATES, 125 MHz, PQFP100 |

| A1415A-PQG100I | FPGA, 200 CLBS, 1500 GATES, PQFP100 |

| A1415A-VQG100C | FPGA, 200 CLBS, 1500 GATES, 125 MHz, PQFP100 |

| A1415A-VQG100I | FPGA, 200 CLBS, 1500 GATES, PQFP100 |

| A1425A-1PLG84C | FPGA, 310 CLBS, 2500 GATES, 150 MHz, PQCC84 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A1415A-PLG84M | 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 Family 1.5K Gates 200 Cells 125MHz 0.8um (CMOS) Technology 5V 84-Pin PLCC 制造商:Microsemi SOC Products Group 功能描述:FPGA ACT 3 1.5K GATES 200 CELLS 125MHZ 0.8UM 5V 84PLCC - Rail/Tube 制造商:Microsemi Corporation 功能描述:IC FPGA 1500 GATES 84-PLCC MIL |

| A1415A-PQ100C | 功能描述:IC FPGA 1500 GATES 100-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ACT™ 3 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A1415A-PQ100I | 功能描述:IC FPGA 1500 GATES 100-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ACT™ 3 产品培训模块:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色产品:Cyclone? IV FPGAs 标准包装:60 系列:CYCLONE® IV GX LAB/CLB数:9360 逻辑元件/单元数:149760 RAM 位总计:6635520 输入/输出数:270 门数:- 电源电压:1.16 V ~ 1.24 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:484-BGA 供应商设备封装:484-FBGA(23x23) |

| A1415A-PQ100M | 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 Family 1.5K Gates 200 Cells 125MHz 0.8um Technology 5V 100-Pin PQFP 制造商:Microsemi Corporation 功能描述:FPGA ACT 3 1.5K GATES 200 CELLS 125MHZ 0.8UM 5V 100PQFP - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA 1500 GATES 100-PQFP MIL |

| A1415A-PQG100C | 功能描述:IC FPGA 1500 GATES 100-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ACT™ 3 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

发布紧急采购,3分钟左右您将得到回复。