- 您现在的位置:买卖IC网 > PDF目录1773 > A3949SLPTR-T (Allegro Microsystems Inc)IC MOTOR DRVR PWM FULL 16TSSOP PDF资料下载

参数资料

| 型号: | A3949SLPTR-T |

| 厂商: | Allegro Microsystems Inc |

| 文件页数: | 5/7页 |

| 文件大小: | 0K |

| 描述: | IC MOTOR DRVR PWM FULL 16TSSOP |

| 标准包装: | 1 |

| 应用: | PWM 电机驱动器 |

| 输出数: | 1 |

| 电流 - 输出: | ±2.8A |

| 电源电压: | 8 V ~ 36 V |

| 工作温度: | -20°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm)裸露焊盘 |

| 供应商设备封装: | 16-TSSOP-EP |

| 包装: | 标准包装 |

| 其它名称: | 620-1132-6 |

�� �

�

�

�A3949�

�DMOS� Full-Bridge� Motor� Driver�

�Functional� Description�

�VREG.� This� supply� voltage� is� used� to� operate� the� sink-�

�side� DMOS� outputs.� VREG� is� internally� monitored� and� in�

�the� case� of� a� fault� condition,� the� outputs� of� the� device� are�

�disabled.� The� VREG� pin� should� be� decoupled� with� a� 0.22� ?� F�

�capacitor� to� ground.�

�Charge� Pump.� The� charge� pump� is� used� to� generate� a�

�supply� above� VBB� to� drive� the� source-side� DMOS� gates.� A�

�0.1� uF� ceramic� monolithic� capacitor� should� be� connected�

�between� CP1� and� CP2� for� pumping� purposes.� A� 0.1� uF�

�ceramic� monolithic� capacitor� should� be� connected� between�

�VCP� and� VBB� to� act� as� a� reservoir� to� run� the� high� side�

�DMOS� devices.� The� VCP� voltage� is� internally� monitored,�

�and� in� the� case� of� a� fault� condition,� the� outputs� of� the� device�

�are� disabled.�

�Shutdown.� In� the� event� of� a� fault� due� to� excessive� junction�

�temperature,� or� low� voltage� on� VCP� or� VREG,� the� outputs� of�

�the� device� are� disabled� until� the� fault� condition� is� removed.�

�At� power-up,� the� UVLO� circuit� disables� the� drivers.�

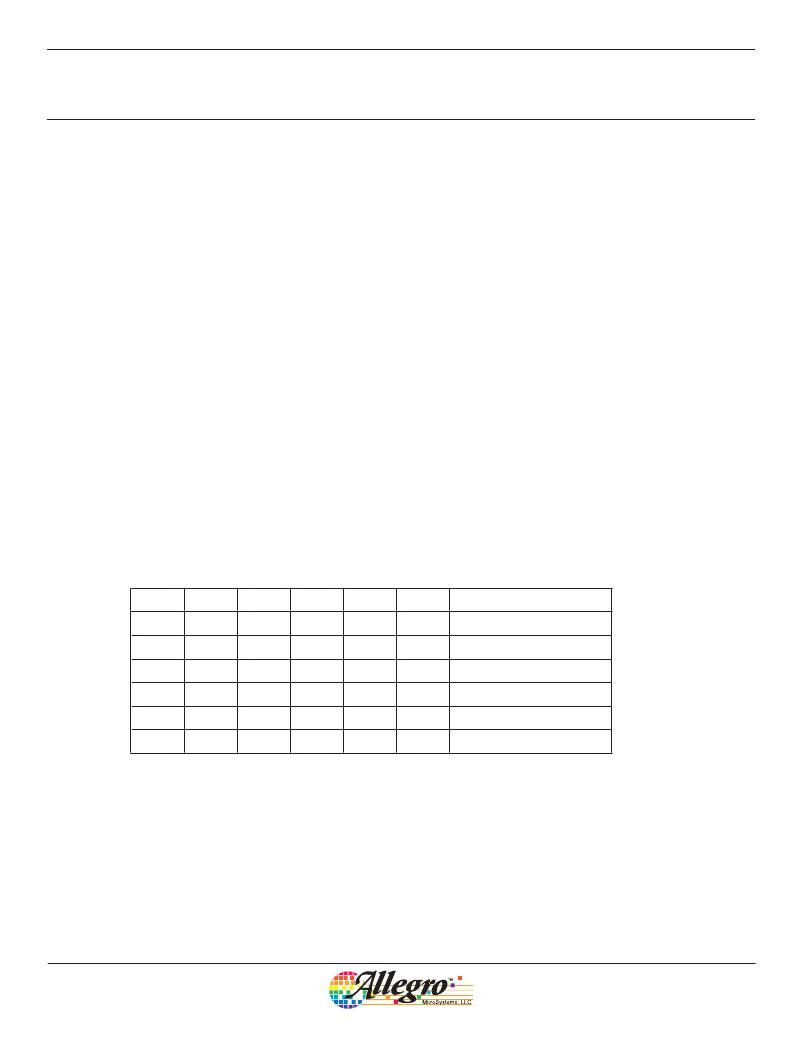

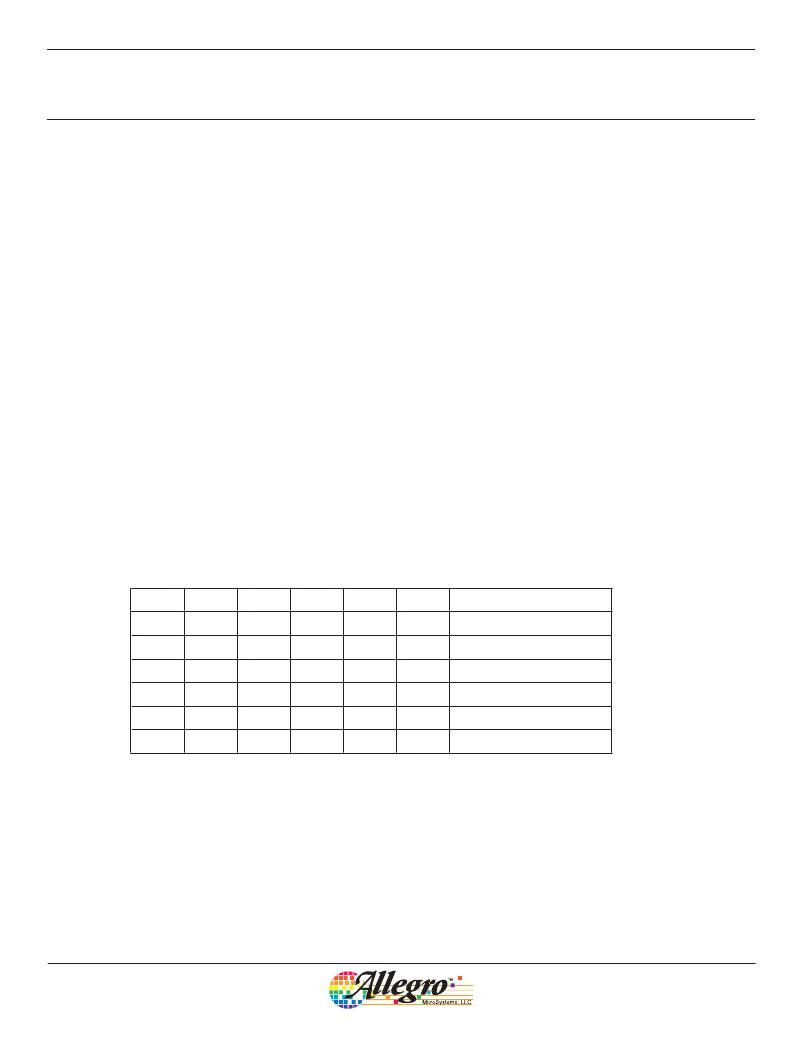

�Control� Logic� Table�

�Sleep� Mode.� Control� input� SLEEP� is� used� to� minimize�

�power� consumption� when� the� A3949� is� not� in� use.� This�

�disables� much� of� the� internal� circuitry,� including� the� low-side�

�gate� supply� and� the� charge� pump.� A� logic� low� on� this� pin�

�puts� the� device� into� Sleep� mode.� A� logic� high� allows� normal�

�operation.� After� coming� out� of� Sleep� mode,� the� user� should�

�wait� 1� ms� before� applying� PWM� signals,� to� allow� the� charge�

�pump� to� stabilize.�

�Braking.� The� braking� function� is� implemented� by� driv-�

�ing� the� device� in� slow� decay� mode� via� the� MODE� pin,� and�

�applying� an� enable� chop� command.� Because� it� is� possible� to�

�drive� current� in� both� directions� through� the� DMOS� switches,�

�this� con� ?� guration� effectively� shorts� out� the� motor-generated�

�BEMF,� as� long� as� the� enable� chop� mode� is� asserted� on� the�

�ENABLE� pin.� The� maximum� current� can� be� approximated�

�by� V� BEMF� /� R� L� .� Care� should� be� taken� to� insure� that� the� maxi-�

�mum� ratings� of� the� device� are� not� exceeded� in� worse� case�

�braking� situations� of� high� speed� and� high� inertial� loads.�

�PHASE� ENABLE� MODE�

�SLEEP�

�OUTA�

�OUTB�

�Function�

�1�

�0�

�X�

�1�

�0�

�X�

�1�

�1�

�0�

�0�

�0�

�X�

�X�

�X�

�1�

�0�

�0�

�X�

�1�

�1�

�1�

�1�

�1�

�0�

�H�

�L�

�L�

�L�

�H�

�Hi-Z�

�L�

�H�

�L�

�H�

�L�

�Hi-Z�

�Forward�

�Reverse�

�Brake� (slow� decay)�

�Fast� decay� SR*�

�Fast� decay� SR*�

�Sleep� mode�

�*� To� prevent� reversal� of� current� during� fast� decay� SR� (synchronous� recti� ?� cation),� the� outputs�

�go� to� the� high� impedance� state� as� the� current� approaches� zero.�

�Allegro� MicroSystems,� LLC�

�115� Northeast� Cutoff�

�Worcester,� Massachusetts� 01615-0036� U.S.A.�

�1.508.853.5000;� www.allegromicro.com�

�5�

�相关PDF资料 |

PDF描述 |

|---|---|

| A3950SLP-T | IC MOTOR DRIVER PWM FULL 16-TSSO |

| A3953SLBTR-T | IC MOTOR DRIVER PWM FULL 16-SOIC |

| A3955SLBTR-T | IC MOTOR DRIVER PWM FULL 16-SOIC |

| A3959SLP-T | IC MOTOR DRIVER PWM FULL 28TSSOP |

| A3966ELBTR-T | IC MOTOR DVR FULL BRIDGE 16SOICW |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A-394SRD | 制造商:Paralight Electronics Co. 功能描述:LED 4DIGIT HT 0.394-INCH SUPERRED |

| A3950 | 制造商:ALLEGRO 制造商全称:Allegro MicroSystems 功能描述:DMOS Full-Bridge Motor Driver |

| A3950_06 | 制造商:ALLEGRO 制造商全称:Allegro MicroSystems 功能描述:DMOS Full-Bridge Motor Driver |

| A3950-0000T | 制造商:3M 制造商全称:3M Electronics 功能描述:100 x 100, PCB Two Row |

| A3950-0010T | 制造商:3M 制造商全称:3M Electronics 功能描述:100 x 100, PCB Two Row |

发布紧急采购,3分钟左右您将得到回复。