- 您现在的位置:买卖IC网 > PDF目录298744 > A42MX36-3VQ100B (Electronic Theatre Controls, Inc.) 40MX and 42MX FPGA Families PDF资料下载

参数资料

| 型号: | A42MX36-3VQ100B |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 40MX and 42MX FPGA Families |

| 中文描述: | 40MX和42MX FPGA系列 |

| 文件页数: | 48/64页 |

| 文件大小: | 854K |

| 代理商: | A42MX36-3VQ100B |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

40MX and 42MX FPGA Families

1- 46

v6.0

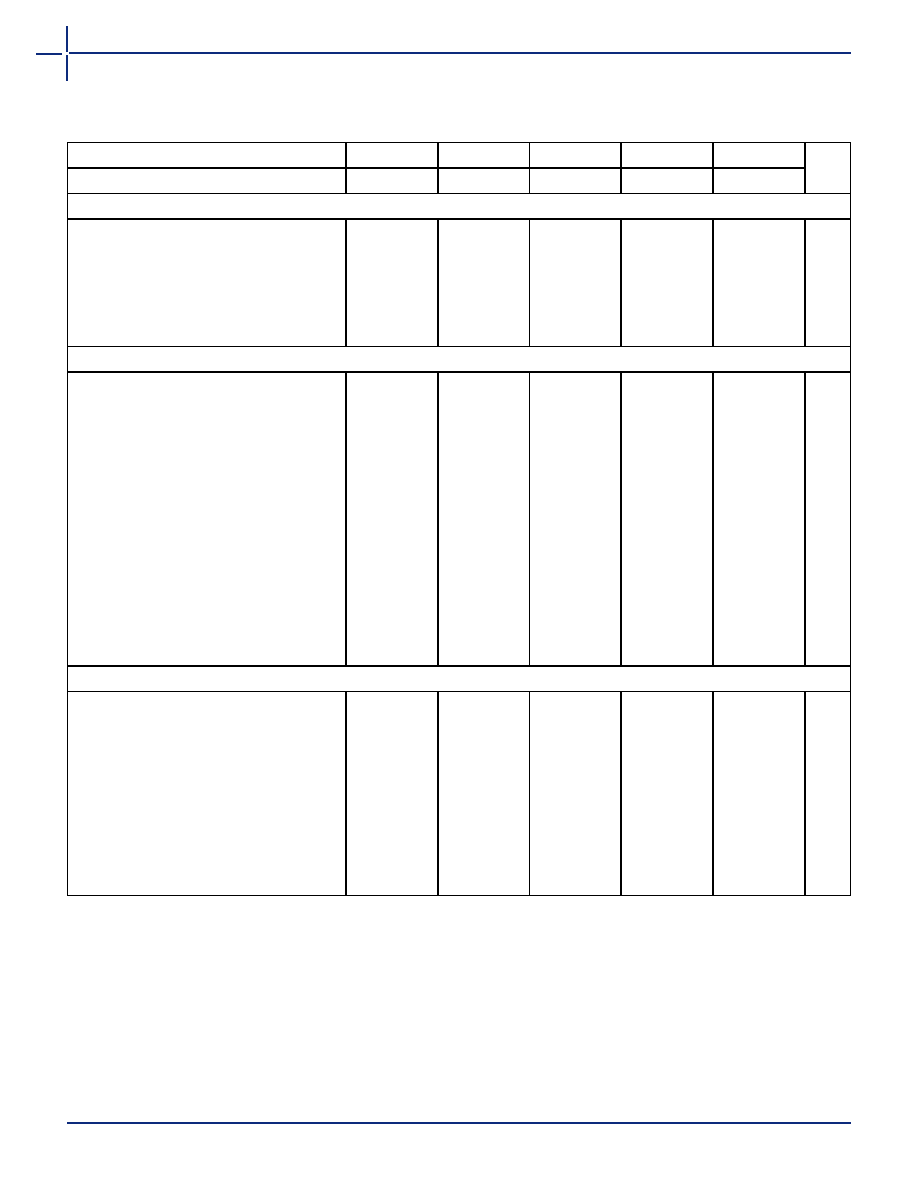

Input Module Predicted Routing Delays1

tIRD1

FO=1 Routing Delay

2.9

3.3

3.8

4.5

6.3

ns

tIRD2

FO=2 Routing Delay

3.6

4.2

4.8

5.6

7.8

ns

tIRD3

FO=3 Routing Delay

4.4

5.0

5.7

6.7

9.4

ns

tIRD4

FO=4 Routing Delay

5.1

5.9

6.7

7.8

11.0

ns

tIRD8

FO=8 Routing Delay

8.0

9.3

10.5

12.4

17.2

ns

Global Clock Network

tCKH

Input LOW to HIGH

FO = 16

FO = 128

6.4

7.4

8.4

9.9

13.8

ns

tCKL

Input HIGH to LOW

FO = 16

FO = 128

6.8

7.8

8.9

10.4

14.6

ns

tPWH

Minimum Pulse

Width HIGH

FO = 16

FO = 128

3.1

3.3

3.6

3.8

4.1

4.3

4.8

5.1

6.7

7.1

ns

tPWL

Minimum Pulse

Width LOW

FO = 16

FO = 128

3.1

3.3

3.6

3.8

4.1

4.3

4.8

5.1

6.7

7.1

ns

tCKSW

Maximum Skew

FO = 16

FO = 128

0.6

0.8

0.6

0.9

0.7

1.0

0.8

1.2

1.6

ns

tP

Minimum Period

FO = 16

FO = 128

6.5

6.8

7.5

7.8

8.5

8.9

10.1

10.4

14.1

14.6

ns

fMAX

Maximum Frequency FO = 16

FO = 128

113

109

105

101

96

92

83

80

50

48

MHz

TTL Output Module Timing4

tDLH

Data-to-Pad HIGH

4.7

5.4

6.1

7.2

10.0

ns

tDHL

Data-to-Pad LOW

5.6

6.4

7.3

8.6

12.0

ns

tENZH

Enable Pad Z to HIGH

5.2

6.0

6.9

8.1

11.3

ns

tENZL

Enable Pad Z to LOW

6.6

7.6

8.6

10.1

14.1

ns

tENHZ

Enable Pad HIGH to Z

11.1

12.8

14.5

17.1

23.9

ns

tENLZ

Enable Pad LOW to Z

8.2

9.5

10.7

12.6

17.7

ns

dTLH

Delta LOW to HIGH

0.03

0.04

0.06

ns/pF

dTHL

Delta HIGH to LOW

0.04

0.05

0.06

0.08

ns/pF

Table 31

A40MX04 Timing Characteristics (Nominal 3.3V Operation) (Continued)

(Worst-Case Commercial Conditions, VCC = 3.0V, TJ = 70°C)

‘–3’ Speed

‘–2’ Speed

‘–1’ Speed

‘Std’ Speed

‘–F’ Speed

Units

Parameter Description

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Notes:

1. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating

device performance. Post-route timing analysis or simulation is required to determine actual performance.

2. Set-up times assume fanout of 3. Further testing information can be obtained from the Timer utility.

3. The hold time for the DFME1A macro may be greater than 0 ns. Use the Timer tool from the Designer software to check the hold

time for this macro.

4. Delays based on 35 pF loading.

相关PDF资料 |

PDF描述 |

|---|---|

| A446-0100-01 | 10 TAP 14 PIN DIP PASSIVE DELAY MODULES |

| A446-0150-01 | 10 TAP 14 PIN DIP PASSIVE DELAY MODULES |

| A446-0200-01 | 10 TAP 14 PIN DIP PASSIVE DELAY MODULES |

| A450-0060-02 | 5 TAP LEADING EDGE CONTROL HIGH -SPEED CMOS DELAY MODULES |

| A450-0070-02 | 5 TAP LEADING EDGE CONTROL HIGH -SPEED CMOS DELAY MODULES |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A42MX36-BG272 | 功能描述:IC FPGA MX SGL CHIP 54K 272-PBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 产品培训模块:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色产品:Cyclone? IV FPGAs 标准包装:60 系列:CYCLONE® IV GX LAB/CLB数:9360 逻辑元件/单元数:149760 RAM 位总计:6635520 输入/输出数:270 门数:- 电源电压:1.16 V ~ 1.24 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:484-BGA 供应商设备封装:484-FBGA(23x23) |

| A42MX36-BG272I | 功能描述:IC FPGA MX SGL CHIP 54K 272-PBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:1 系列:ProASICPLUS LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:129024 输入/输出数:248 门数:600000 电源电压:2.3 V ~ 2.7 V 安装类型:表面贴装 工作温度:- 封装/外壳:352-BFCQFP,带拉杆 供应商设备封装:352-CQFP(75x75) |

| A42MX36-BG272M | 制造商:Microsemi Corporation 功能描述:FPGA 42MX Family 54K Gates 1184 Cells 79MHz/131MHz 0.45um Technology 3.3V/5V 272-Pin BGA 制造商:Microsemi Corporation 功能描述:FPGA 54K GATES 1184 CELLS 79MHZ/131MHZ 0.45UM 3.3V/5V 272BGA - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA 202 I/O 272PBGA 制造商:Microsemi Corporation 功能描述:IC FPGA MX SGL CHIP 54K 272-PBGA |

| A42MX36-BGG272 | 功能描述:IC FPGA MX SGL CHIP 54K 272-PBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 产品培训模块:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色产品:Cyclone? IV FPGAs 标准包装:60 系列:CYCLONE® IV GX LAB/CLB数:9360 逻辑元件/单元数:149760 RAM 位总计:6635520 输入/输出数:270 门数:- 电源电压:1.16 V ~ 1.24 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:484-BGA 供应商设备封装:484-FBGA(23x23) |

| A42MX36-BGG272I | 功能描述:IC FPGA MX SGL CHIP 54K 272-PBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:1 系列:ProASICPLUS LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:129024 输入/输出数:248 门数:600000 电源电压:2.3 V ~ 2.7 V 安装类型:表面贴装 工作温度:- 封装/外壳:352-BFCQFP,带拉杆 供应商设备封装:352-CQFP(75x75) |

发布紧急采购,3分钟左右您将得到回复。