参数资料

| 型号: | A54SX32-TQG176I |

| 厂商: | Microsemi SoC |

| 文件页数: | 24/64页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SX 48K GATES 176-TQFP |

| 标准包装: | 40 |

| 系列: | SX |

| LAB/CLB数: | 2880 |

| 输入/输出数: | 147 |

| 门数: | 48000 |

| 电源电压: | 3 V ~ 3.6 V,4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 176-LQFP |

| 供应商设备封装: | 176-TQFP(24x24) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

SX Family FPGAs

1- 26

v3.2

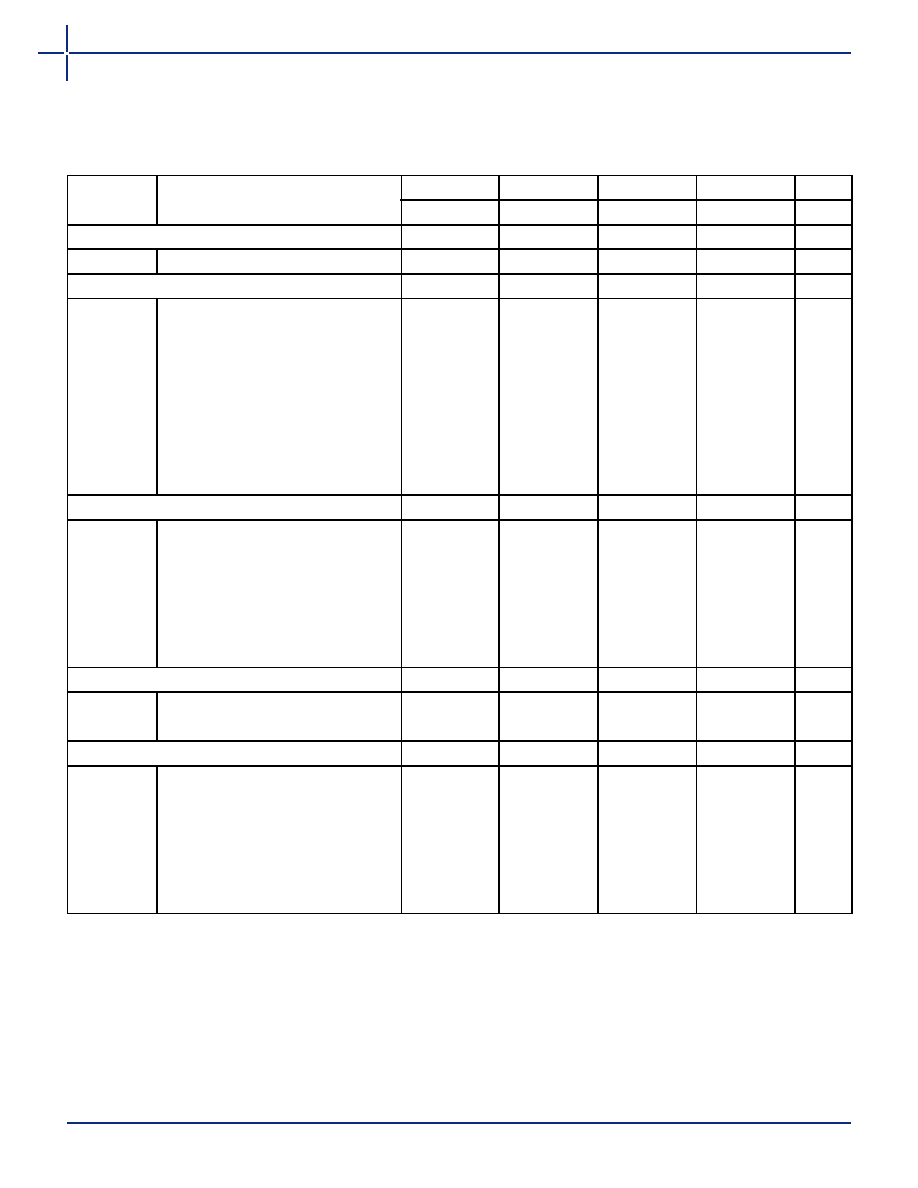

A54SX16 Timing Characteristics

Table 1-18 A54SX16 Timing Characteristics

(Worst-Case Commercial Conditions, VCCR = 4.75 V, VCCA ,VCCI = 3.0 V, TJ = 70°C)

Parameter

Description

'–3' Speed

'–2' Speed

'–1' Speed

'Std' Speed

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Units

C-Cell Propagation Delays1

tPD

Internal Array Module

0.6

0.7

0.8

0.9

ns

Predicted Routing Delays2

tDC

FO = 1 Routing Delay, Direct Connect

0.1

ns

tFC

FO = 1 Routing Delay, Fast Connect

0.3

0.4

0.5

ns

tRD1

FO = 1 Routing Delay

0.3

0.4

0.5

ns

tRD2

FO = 2 Routing Delay

0.6

0.7

0.8

0.9

ns

tRD3

FO = 3 Routing Delay

0.8

0.9

1.0

1.2

ns

tRD4

FO = 4 Routing Delay

1.0

1.2

1.4

1.6

ns

tRD8

FO = 8 Routing Delay

1.9

2.2

2.5

2.9

ns

tRD12

FO = 12 Routing Delay

2.8

3.2

3.7

4.3

ns

R-Cell Timing

tRCO

Sequential Clock-to-Q

0.8

1.1

1.2

1.4

ns

tCLR

Asynchronous Clear-to-Q

0.5

0.6

0.7

0.8

ns

tPRESET

Asynchronous Preset-to-Q

0.7

0.8

0.9

1.0

ns

tSUD

Flip-Flop Data Input Set-Up

0.5

0.7

0.8

ns

tHD

Flip-Flop Data Input Hold

0.0

ns

tWASYN

Asynchronous Pulse Width

1.4

1.6

1.8

2.1

ns

Input Module Propagation Delays

tINYH

Input Data Pad-to-Y HIGH

1.5

1.7

1.9

2.2

ns

tINYL

Input Data Pad-to-Y LOW

1.5

1.7

1.9

2.2

ns

Predicted Input Routing Delays2

tIRD1

FO = 1 Routing Delay

0.3

0.4

0.5

ns

tIRD2

FO = 2 Routing Delay

0.6

0.7

0.8

0.9

ns

tIRD3

FO = 3 Routing Delay

0.8

0.9

1.0

1.2

ns

tIRD4

FO = 4 Routing Delay

1.0

1.2

1.4

1.6

ns

tIRD8

FO = 8 Routing Delay

1.9

2.2

2.5

2.9

ns

tIRD12

FO = 12 Routing Delay

2.8

3.2

3.7

4.3

ns

Notes:

1. For dual-module macros, use tPD + tRD1 + tPDn, tRCO + tRD1 + tPDn, or tPD1 + tRD1 + tSUD, whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating

device performance.

Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route

timing is based on actual routing delay measurements performed on the device prior to shipment.

3. Delays based on 35 pF loading, except tENZL and tENZH. For tENZL and tENZH, the loading is 5 pF.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT71V256SA15YG8 | IC SRAM 256KBIT 15NS 28SOJ |

| A54SX32-1TQ176 | IC FPGA SX 48K GATES 176-TQFP |

| AT25256B-MAHL-T | IC EEPROM 256KBIT 20MHZ 8UDFN |

| CAT24C512ZI-T3 | IC EEPROM 512KB I2C SER 8MSOP |

| DS24B33+ | IC EEPROM 4KBIT TO92 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A54SX72A-1CQ208 | 功能描述:IC FPGA SX-A 108K GATES 208-CQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:SX-A 标准包装:1 系列:ProASICPLUS LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:129024 输入/输出数:248 门数:600000 电源电压:2.3 V ~ 2.7 V 安装类型:表面贴装 工作温度:- 封装/外壳:352-BFCQFP,带拉杆 供应商设备封装:352-CQFP(75x75) |

| A54SX72A-1CQ208B | 功能描述:IC FPGA SX-A 108K 208-CQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:SX-A 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| A54SX72A-1CQ208M | 制造商:Microsemi Corporation 功能描述:FPGA SX-A 72K GATES 4024 CELLS 250MHZ 0.25UM/0.22UM 2.5V 208 - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA 108K GATES 208CQFP 制造商:Microsemi Corporation 功能描述:IC FPGA 171 I/O 208CQFP |

| A54SX72A-1CQ256 | 功能描述:IC FPGA SX-A 108K 256-CQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:SX-A 标准包装:1 系列:ProASICPLUS LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:129024 输入/输出数:248 门数:600000 电源电压:2.3 V ~ 2.7 V 安装类型:表面贴装 工作温度:- 封装/外壳:352-BFCQFP,带拉杆 供应商设备封装:352-CQFP(75x75) |

| A54SX72A-1CQ256B | 功能描述:IC FPGA SX-A 108K 256-CQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:SX-A 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。