参数资料

| 型号: | AD1853JRSZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/16页 |

| 文件大小: | 0K |

| 描述: | IC DAC STEREO 24BIT 28SSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 47 |

| 位数: | 24 |

| 数据接口: | DSP,I²S,串行,SPI? |

| 转换器数目: | 2 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 200mW |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 28-SSOP |

| 包装: | 管件 |

| 输出数目和类型: | 4 电流,单极 |

| 采样率(每秒): | 192k |

| 产品目录页面: | 781 (CN2011-ZH PDF) |

REV. A

AD1853

–9–

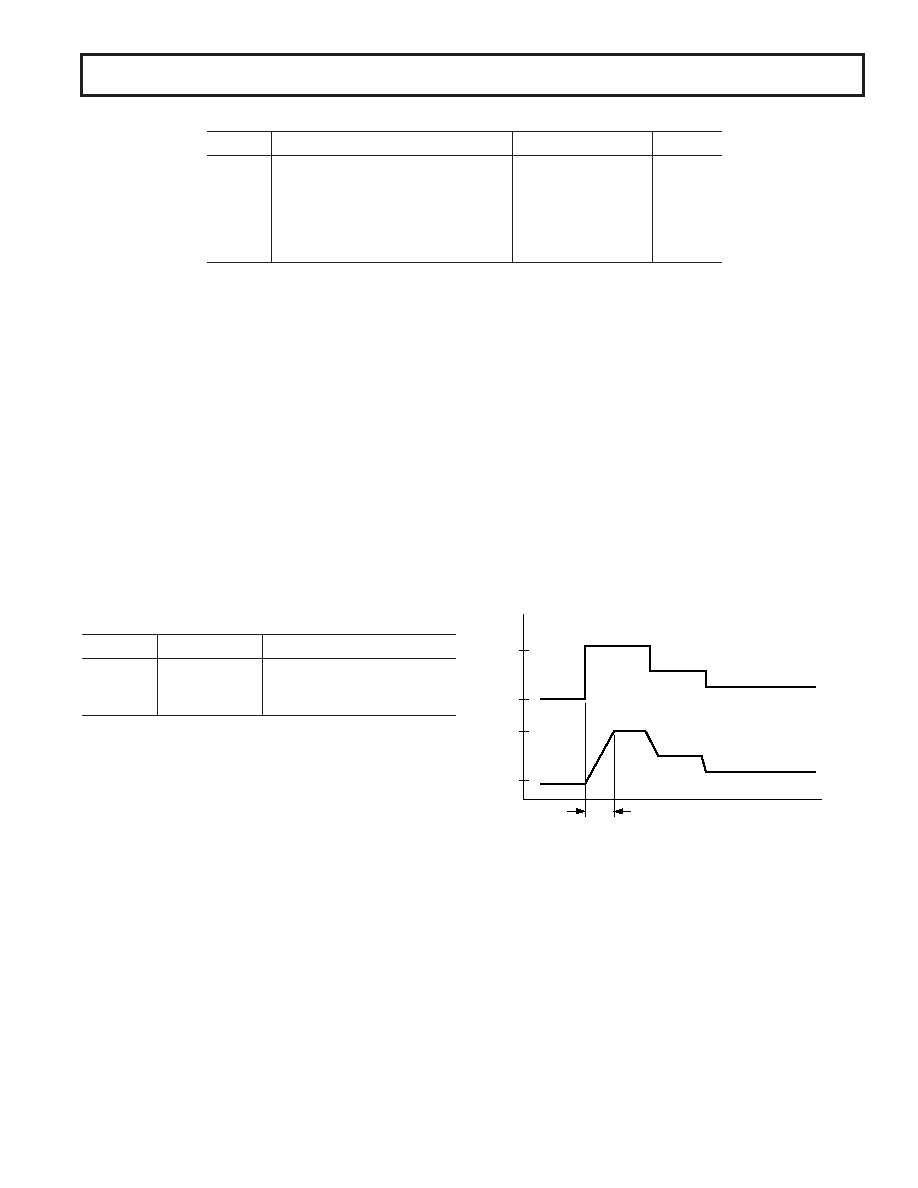

Table III. Digital Timing

Min

Units

tCCH

CCLK HI Pulsewidth

40

ns

tCCL

CCLK LOW Pulsewidth

40

ns

tCSU

CDATA Setup Time

10

ns

tCHD

CDATA Hold Time

10

ns

tCLL

CLATCH LOW Pulsewidth

10

ns

tCLH

CLATCH HI Pulsewidth

10

ns

SPI REGISTER DEFINITIONS

The SPI port allows flexible control of many chip parameters.

It is organized around three registers; a LEFT-CHANNEL

VOLUME register, a RIGHT-CHANNEL VOLUME register

and a CONTROL register. Each WRITE operation to the

AD1853 SPI control port requires 16 bits of serial data in

MSB-first format. The bottom two bits are used to select one

of three registers, and the top 14 bits are then written to that

register. This allows a write to one of the three registers in a

single 16-bit transaction.

The SPI CCLK signal is used to clock in the data. The incom-

ing data should change on the falling edge of this signal. At the

end of the 16 CCLK periods, the CLATCH signal should rise

to latch the data internally into the AD1853.

Register Addresses

The lowest two bits of the 16-bit input word are decoded as

follows to set the register into which the upper 14 bits will be

written.

Bit 1

Bit 0

Register

00Volume Left

10Volume Right

01Control Register

VOLUME LEFT and VOLUME RIGHT Registers

A write operation to the left or right volume registers will acti-

vate the “auto-ramp” clickless volume control feature of the

AD1853. This feature works as follows. The upper 10 bits of

the volume control word will be incremented or decremented by

1 at a rate equal to the input sample rate. The bottom 4 bits are

not fed into the auto-ramp circuit and thus take effect immedi-

ately. This arrangement gives a worst-case ramp time of about

1024/FS for step changes of more than 60 dB, which has been

determined by listening tests to be optimal in terms of pre-

venting the perception of a “click” sound on large volume

changes. See Figure 8 for a graphical description of how the

volume changes as a function of time.

The 14-bit volume control word is used to multiply the signal,

and therefore the control characteristic is linear, not dB. A con-

stant dB/step characteristic can be obtained by using a lookup

table in the microprocessor that is writing to the SPI port.

20ms

TIME

–60

0

LEVEL

–

dB

VOLUME REQUEST REGISTER

ACTUAL VOLUME REGISTER

Figure 8. Smooth Volume Control

相关PDF资料 |

PDF描述 |

|---|---|

| MS3450L36-10S | CONN RCPT 48POS WALL MNT W/SCKT |

| D38999/20KG41SB | CONN RCPT 41POS WALL MNT W/SCKT |

| LTC2625IGN-1#PBF | IC DAC 12BIT R-R OCT 16SSOP |

| GTC01CF-24-67P | CONN RCPT 19POS INLINE W/PINS |

| MS3450LS22-22S | CONN RCPT 4POS WALL MNT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1853JRSZRL | 功能描述:IC DAC STEREO 192KHZ 5V 28SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

| AD1854 | 制造商:AD 制造商全称:Analog Devices 功能描述:Stereo, 96 kHz, Multibit DAC |

| AD1854JRS | 制造商:Analog Devices 功能描述:DAC 2-CH Delta-Sigma 24-bit 28-Pin SSOP 制造商:Rochester Electronics LLC 功能描述:STEREO,96KHZ, MULTIBIT SIGMA DELTA DAC - Bulk |

| AD1854JRSRL | 制造商:Analog Devices 功能描述:DAC 2-CH Delta-Sigma 24-bit 28-Pin SSOP T/R 制造商:Rochester Electronics LLC 功能描述:STEREO,96KHZ, MULTIBIT SIGMA DELTA DAC - Bulk |

| AD1854JRSZ | 功能描述:IC DAC STEREO 96KHZ 5V 28SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 设置时间:4µs 位数:12 数据接口:串行 转换器数目:2 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-uMAX 包装:管件 输出数目和类型:2 电压,单极 采样率(每秒):* 产品目录页面:1398 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。