- 您现在的位置:买卖IC网 > PDF目录10938 > AD1937WBSTZ-RL (Analog Devices Inc)IC CODEC 4/ADC DIFF OUT 64-LQFP PDF资料下载

参数资料

| 型号: | AD1937WBSTZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/36页 |

| 文件大小: | 0K |

| 描述: | IC CODEC 4/ADC DIFF OUT 64-LQFP |

| 标准包装: | 1,500 |

| 类型: | 通用 |

| 数据接口: | 串行 |

| 分辨率(位): | 24 b |

| ADC / DAC 数量: | 4 / 8 |

| 三角积分调变: | 是 |

| S/N 比,标准 ADC / DAC (db): | 96 / 96 |

| 动态范围,标准 ADC / DAC (db): | 105 / 110 |

| 电压 - 电源,模拟: | 3 V ~ 3.6 V |

| 电压 - 电源,数字: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD1937

Rev. B | Page 19 of 36

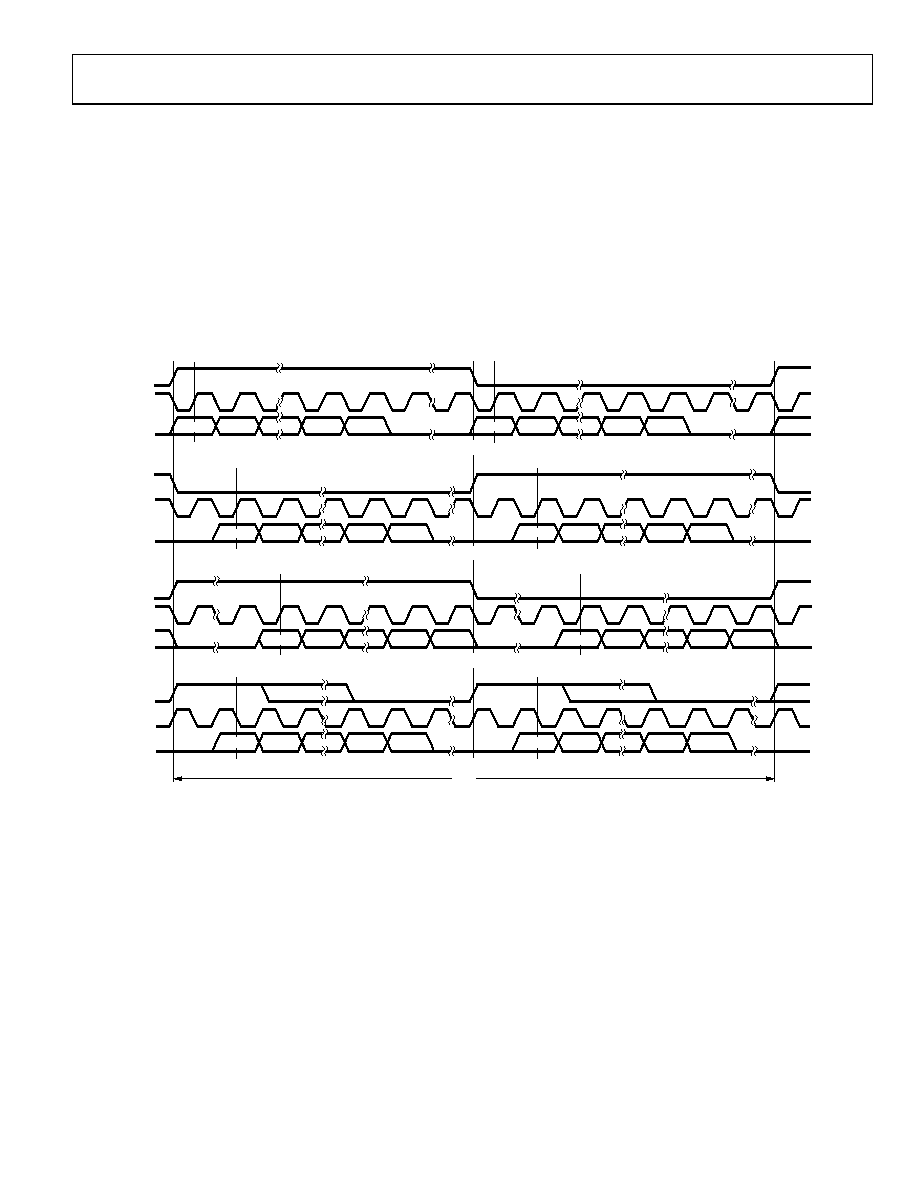

SERIAL DATA PORTS—DATA FORMAT

The eight DAC channels use a common serial bit clock (DBCLK)

and a common left-right framing clock (DLRCLK) in the serial

data port. The four ADC channels use a common serial bit

clock (ABCLK) and left-right framing clock (ALRCLK) in the

serial data port. The clock signals are all synchronous with the

sample rate. The normal stereo serial modes are shown in

The ADC and DAC serial data modes default to I2S stereo.

The ports can also be programmed for left-justified stereo,

right-justified stereo, and TDM modes. The word width is

24 bits by default and can be set to 16 or 20 bits in the DAC

Control 2 and ADC Control 1 registers. The DAC serial formats

are programmable in the DAC Control 0 register. The polarity of

DBCLK and DLRCLK is programmable in the DAC Control 1 reg-

ister. The ADC serial format is programmable in ADC Control 1

register. The ABCLK and ALRCLK clock polarities are pro-

Figure 15 all of the clocks are shown with their normal polarity.

Both DAC and ADC serial ports can be programmed to become

the bus masters according to DAC Control 1 and ADC Control 2

registers. By default, both ADC and DAC serial ports are in the

slave mode.

LRCLK

BCLK

SDATA

LRCLK

BCLK

SDATA

LRCLK

BCLK

SDATA

LSB

LEFT CHANNEL

RIGHT CHANNEL

LSB

LEFT CHANNEL

RIGHT CHANNEL

LEFT CHANNEL

MSB

LEFT-JUSTIFIED MODE—16 BITS TO 24 BITS PER CHANNEL

MSB

RIGHT-JUSTIFIED MODE—SELECT NUMBER OF BITS PER CHANNEL

DSP MODE—16 BITS TO 24 BITS PER CHANNEL

I2S-JUSTIFIED MODE—16 BITS TO 24 BITS PER CHANNEL

LRCLK

BCLK

SDATA

LSB

NOTES

1. DSP MODE DOES NOT IDENTIFY CHANNEL.

2. LRCLK NORMALLY OPERATES AT

fS EXCEPT FOR DSP MODE, WHICH IS 2 × fS.

3. BCLK FREQUENCY IS NORMALLY 64 × LRCLK BUT MAY BE OPERATED IN BURST MODE.

MSB

1/

fS

0

74

14-

02

4

Figure 15. Stereo Modes

相关PDF资料 |

PDF描述 |

|---|---|

| AD1938WBSTZ-RL | IC CODEC 24BIT 4ADC/8DAC 48LQFP |

| AD1938YSTZRL | IC CODEC 24BIT 4ADC/8DAC 48LQFP |

| MCF5213LCVM80 | IC MCU 256K FLASH 80MHZ 81MAPBGA |

| VI-BNL-IW-B1 | CONVERTER MOD DC/DC 28V 100W |

| CS4245-DQZ | IC CODEC AUD STER 104DB 48LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1937XSTZ | 制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC |

| AD1937XSTZRL | 制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC |

| AD1938 | 制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24-Bit CODEC |

| AD1938WBSTZ | 功能描述:IC CODEC 24BIT 4ADC/8DAC 48LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| AD1938WBSTZ-RL | 功能描述:IC CODEC 24BIT 4ADC/8DAC 48LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。