参数资料

| 型号: | AD1938WBSTZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 30/32页 |

| 文件大小: | 0K |

| 描述: | IC CODEC 24BIT 4ADC/8DAC 48LQFP |

| 标准包装: | 1 |

| 类型: | 通用 |

| 数据接口: | 串行 |

| 分辨率(位): | 24 b |

| ADC / DAC 数量: | 4 / 8 |

| 三角积分调变: | 是 |

| S/N 比,标准 ADC / DAC (db): | 94 / 94 |

| 动态范围,标准 ADC / DAC (db): | 105 / 106 |

| 电压 - 电源,模拟: | 3 V ~ 3.6 V |

| 电压 - 电源,数字: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页

Data Sheet

AD1938

Rev. E | Page 7 of 32

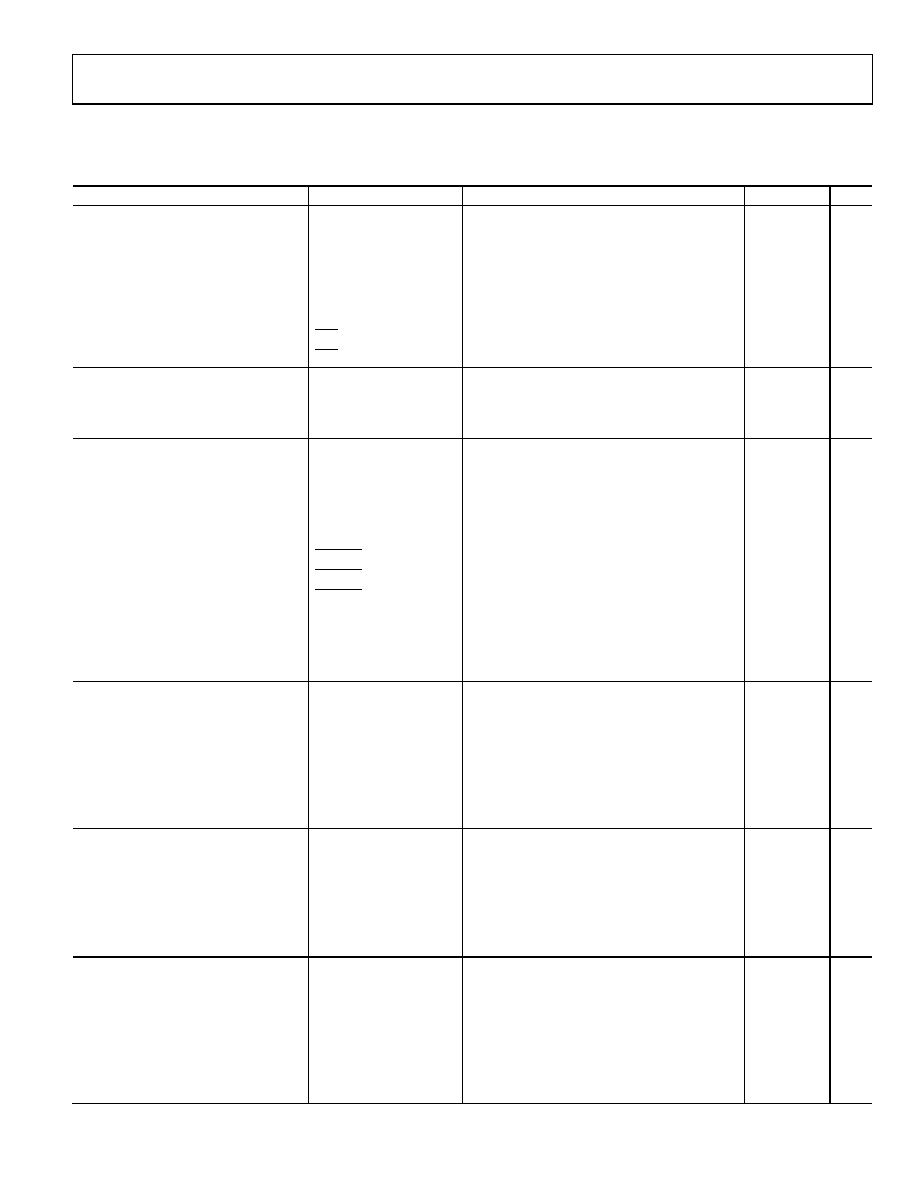

TIMING SPECIFICATIONS

40°C < TC < +125°C, DVDD = 3.3 V ± 10%.

Table 7.

Parameter

Condition

Comments

Min

Max

Unit

INPUT MASTER CLOCK (MCLK) AND RESET

tMH

MCLK duty cycle

DAC/ADC clock source = PLL clock @ 256 fS,

384 fS, 512 fS, and 768 fS

40

60

%

tMH

DAC/ADC clock source = direct MCLK @ 512 fS

(bypass on-chip PLL)

40

60

%

fMCLK

MCLK frequency

PLL mode, 256 fS reference

6.9

13.8

MHz

fMCLK

Direct 512 fS mode

27.6

MHz

tPDR

RST low

15

ns

tPDRR

RST recovery

Reset to active output

4096

tMCLK

PLL

Lock time

MCLK and LR clock input

10

ms

256 fS VCO Clock, Output Duty Cycle,

MCLKO/XO Pin

40

60

%

SPI PORT

See Figure 11

tCCH

CCLK high

35

ns

tCCL

CCLK low

35

ns

fCCLK

CCLK frequency

10

MHz

tCDS

CIN setup

To CCLK rising

10

ns

tCDH

CIN hold

From CCLK rising

10

ns

tCLS

CLATCH setup

To CCLK rising

10

ns

tCLH

CLATCH hold

From CCLK rising

10

ns

tCLH

CLATCH high

Not shown in Figure 11

10

ns

tCOE

COUT enable

From CCLK falling

30

ns

tCOD

COUT delay

From CCLK falling

30

ns

tCOH

COUT hold

From CCLK falling, not shown in Figure 11

30

ns

tCOTS

COUT tristate

From CCLK falling

30

ns

DAC SERIAL PORT

See Figure 24

tDBH

DBCLK high

Slave mode

10

ns

tDBL

DBCLK low

Slave mode

10

ns

tDLS

DLRCLK setup

To DBCLK rising, slave mode

10

ns

tDLH

DLRCLK hold

From DBCLK rising, slave mode

5

ns

tDLS

DLRCLK skew

From DBCLK falling, master mode

8

+8

ns

tDDS

DSDATA setup

To DBCLK rising

10

ns

tDDH

DSDATA hold

From DBCLK rising

5

ns

ADC SERIAL PORT

See Figure 25

tABH

ABCLK high

Slave mode

10

ns

tABL

ABCLK low

Slave mode

10

ns

tALS

ALRCLK setup

To ABCLK rising, slave mode

10

ns

tALH

ALRCLK hold

From ABCLK rising, slave mode

5

ns

tALS

ALRCLK skew

From ABCLK falling, master mode

8

+8

ns

tABDD

ASDATA delay

From ABCLK falling

18

ns

AUXILIARY INTERFACE

tAXDS

AAUXDATA setup

To AUXBCLK rising

10

ns

tAXDH

AAUXDATA hold

From AUXBCLK rising

5

ns

tDXDD

DAUXDATA delay

From AUXBCLK falling

18

ns

tXBH

AUXBCLK high

10

ns

tXBL

AUXBCLK low

10

ns

tDLS

AUXLRCLK setup

To AUXBCLK rising

10

ns

tDLH

AUXLRCLK hold

From AUXBCLK rising

5

ns

相关PDF资料 |

PDF描述 |

|---|---|

| AD1939WBSTZ-RL | AUDIO CODEC W/ON CHIP 4ADC 8DAC |

| AD1953YSTZ | IC DSP DAC AUDIO3CH/26BIT 48LQFP |

| AD1954YSTZRL | IC DAC AUDIO 3CHAN 26BIT 48LQFP |

| AD1955ARSZRL | IC DAC AUDIO 16-24BIT 28SSOP |

| AD1970JSTZ | IC ENCODER BTSC W/CODEC 48-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1938WBSTZ-RL | 功能描述:IC CODEC 24BIT 4ADC/8DAC 48LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| AD1938XSTZ | 制造商:Analog Devices 功能描述:AUD CODEC 4ADC / 8DAC 24BIT 48LQFP - Trays |

| AD1938XSTZRL | 制造商:Analog Devices 功能描述:AUD CODEC 4ADC / 8DAC 24BIT 48LQFP - Tape and Reel |

| AD1938YSTZ | 功能描述:IC CODEC 24BIT 4ADC/8DAC 48LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| AD1938YSTZRL | 功能描述:IC CODEC 24BIT 4ADC/8DAC 48LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。