参数资料

| 型号: | AD5222BRZ10 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/10页 |

| 文件大小: | 0K |

| 描述: | IC POT DGTL DUAL 128POS 14-SOIC |

| 标准包装: | 56 |

| 接片: | 128 |

| 电阻(欧姆): | 10k |

| 电路数: | 2 |

| 温度系数: | 标准值 -35 ppm/°C |

| 存储器类型: | 易失 |

| 接口: | 4 线串行(芯片选择,递增,增/减) |

| 电源电压: | 2.7 V ~ 5.5 V,±2.3 V ~ 2.7 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 14-SOICN |

| 包装: | 管件 |

–2–

REV. 0

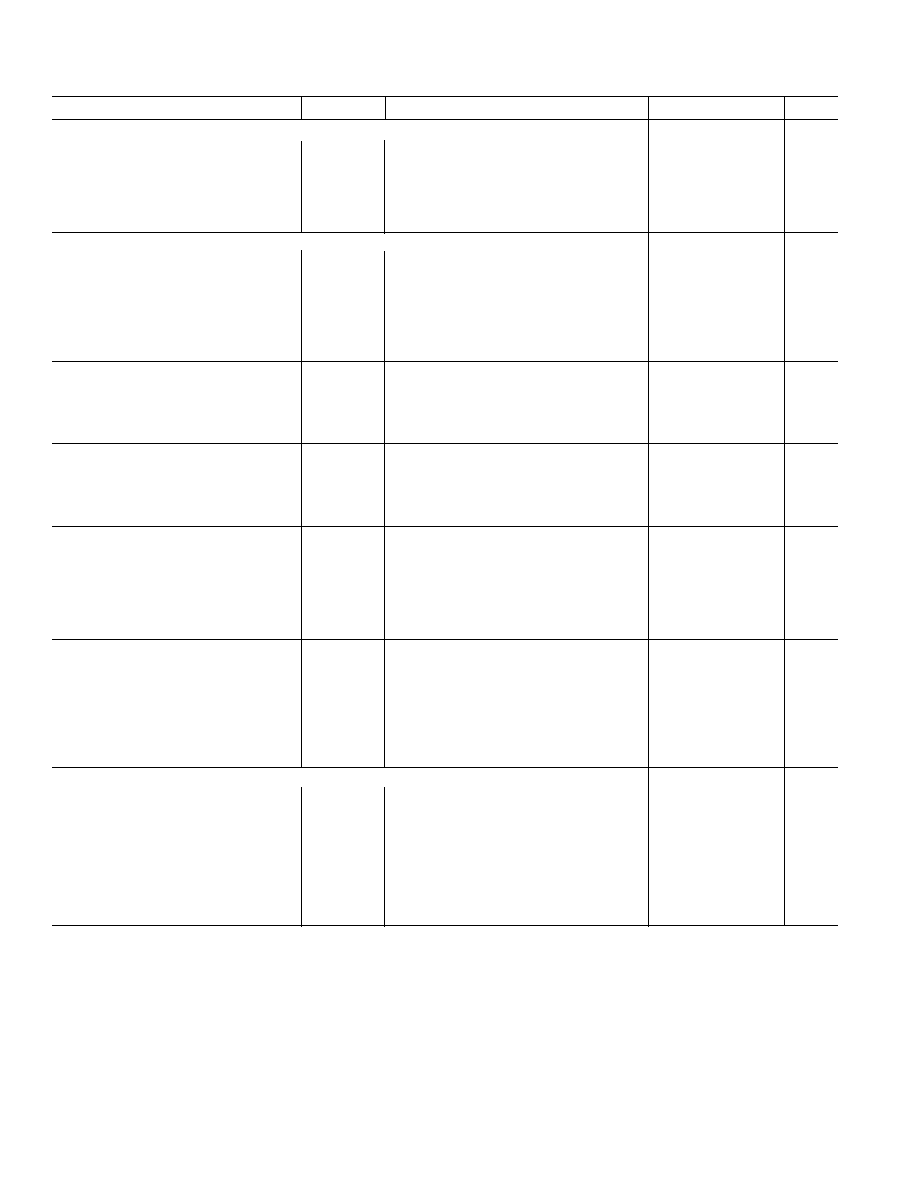

AD5222–SPECIFICATIONS

(VDD = 3 V

10% or 5 V

10%, VSS = 0 V, VA = +VDD, VB = 0 V, –40 C < TA < +85 C,

unless otherwise noted.)

Parameter

Symbol

Condition

Min

Typ

1

Max

Unit

DC CHARACTERISTICS RHEOSTAT MODE (Specifications Apply to All VRs)

Resistor Differential NL

2

R-DNL

RWB, VA = NC

–1

±1/4 +1

LSB

Resistor Nonlinearity

2

R-INL

RWB, VA = NC

–1

±0.4 +1

LSB

Nominal Resistor Tolerance

RV

AB = VDD, Wiper = No Connect, TA = 25°C

–30

+30

%

Resistance Temperature Coefficient

RAB/TVAB = VDD, Wiper = No Connect

–35

ppm/

°C

Wiper Resistance

3

R

W

I

W = VDD /R, VDD = 3 V or 5 V

45

100

Nominal Resistance Match

R/R

O

CH 1 to 2, VAB = VDD, TA = 25°C0.2

1

%

DC CHARACTERISTICS POTENTIOMETER DIVIDER MODE (Specifications Apply to All VRs)

Resolution

N

7

Bits

Integral Nonlinearity

4

INL

RAB = 10 k, 50 k, or 100 k

–1

±1/4 +1

LSB

INL

RAB = 1 M

–2

±1/2 +2

LSB

Differential Nonlinearity

4

DNL

–1

±1/4 +1

LSB

Voltage Divider Temperature Coefficient

V

W/T

Code = 40H

20

ppm/

°C

Full-Scale Error

VWFSE

Code = 7FH

–1

–0.5

+0

LSB

Zero-Scale Error

VWZSE

Code = 00H

0

0.5

1

LSB

RESISTOR TERMINALS

Voltage Range

5

VA, B, W

VSS

VDD

V

Capacitance

6 A, B

C

A, B

f = 1 MHz, Measured to GND, Code = 40

H

45

pF

Capacitance

6 WC

W

f = 1 MHz, Measured to GND, Code = 40H

60

pF

Common-Mode Leakage

ICM

VA = VB = VW

1nA

DIGITAL INPUTS AND OUTPUTS

Input Logic High

VIH

VDD = 5 V/3 V

2.4/2.1

V

Input Logic Low

VIL

VDD = 5 V/3 V

0.8/0.6 V

Input Current

IIL

VIN = 0 V or 5 V

±1

A

Input Capacitance

6

CIL

5pF

POWER SUPPLIES

Power Single-Supply Range

VDD RANGE

VSS = 0 V

2.7

5.5

V

Power Dual-Supply Range

VDD/SS RANGE

±2.3

±2.7

V

Positive Supply Current

IDD

VIH = 5 V or VIL = 0 V

15

40

A

Negative Supply Current

ISS

VSS = –2.5 V, VDD = +2.7 V

15

40

A

Power Dissipation

7

PDISS

VIH = 5 V or VIL = 0 V, VDD = 5 V

150

400

W

Power Supply Sensitivity

PSS

0.002 0.05

%/%

DYNAMIC CHARACTERISTICS

6, 8, 9

Bandwidth –3 dB

BW_10K

RAB = 10 k, Code = 40H

1000

kHz

BW_50K

RAB = 50 k, Code = 40H

180

kHz

BW_100K

RAB = 100 k, Code = 40H

78

kHz

BW_1M

RAB = 500 k, Code = 40H

7kHz

Total Harmonic Distortion

THD

W

V

A = 1 V rms + 2 V dc, VB = 2 V dc, f = 1 kHz

0.005

%

VW Settling Time

tS

RAB = 10 k, ± 1 LSB Error Band

2

s

Resistor Noise Voltage

eN_WB

RWB = 5 k, f = 1 kHz

14

nV

√Hz

INTERFACE TIMING CHARACTERISTICS (Applies to All Parts)

6, 10

Input Clock Pulsewidth

tCH, tCL

Clock Level High or Low

30

ns

CS to CLK Setup Time

tCSS

20

ns

CS Rise to CLK Hold Time

tCSH

20

ns

U/

D to Clock Fall Setup Time

tUDS

10

ns

U/

D to Clock Fall Hold Time

tUDH

30

ns

DACSEL to Clock Fall Setup Time

tDSS

20

ns

DACSEL to Clock Fall Hold Time

tDSH

30

ns

MODE to Clock Fall Setup Time

tMDS

20

ns

MODE to Clock Fall Hold Time

tMDH

40

ns

NOTES

1Typicals represent average readings at 25

°C, V

DD = 5 V.

2Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions.

R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. See Figure 22 test circuit.

3Wiper resistance is not measured on the R

AB = 1 M models.

4INL and DNL are measured at V

W with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. V A = VDD and VB = 0 V. DNL

specification limits of

±1 LSB maximum are guaranteed monotonic operating conditions. See Figure 21 test circuit.

5Resistor Terminals A, B, W have no limitations on polarity with respect to each other.

6Guaranteed by design and not subject to production test.

7P

DISS is calculated from (IDD × V DD). CMOS logic level inputs result in minimum power dissipation.

8Bandwidth, noise and settling time are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest bandwidth.

The highest R value results in the minimum overall power consumption.

9All dynamic characteristics use V

DD = 5 V.

10See timing diagram for location of measured values. All input control voltages are specified with t

R = tF = 2.5 ns (10% to 90% of +3 V) and timed from a voltage level

of 1.5 V. Switching characteristics are measured using both VDD = 5 V or VDD = 3 V.

Specifications subject to change without notice.

相关PDF资料 |

PDF描述 |

|---|---|

| DS1100Z-35+ | IC DELAY LINE 5TAP 35NS 8-SOIC |

| VE-2WD-MW | CONVERTER MOD DC/DC 85V 100W |

| DS1100Z-60+ | IC DELAY LINE 5TAP 60NS 8-SOIC |

| DS1100Z-100+ | IC DELAY LINE 5TAP 100NS 8-SOIC |

| VE-2W4-MX-B1 | CONVERTER MOD DC/DC 48V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5222BRZ100 | 功能描述:IC POT DGTL DUAL 128POS 14SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数字电位器 系列:- 标准包装:2,500 系列:XDCP™ 接片:256 电阻(欧姆):100k 电路数:1 温度系数:标准值 ±300 ppm/°C 存储器类型:非易失 接口:I²C(设备位址) 电源电压:2.7 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-TSSOP(0.173",4.40mm 宽) 供应商设备封装:14-TSSOP 包装:带卷 (TR) |

| AD5222BRZ10-REEL7 | 功能描述:IC POT DGTL DUAL 128POS 14SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数字电位器 系列:- 标准包装:3,000 系列:DPP 接片:32 电阻(欧姆):10k 电路数:1 温度系数:标准值 300 ppm/°C 存储器类型:非易失 接口:3 线串行(芯片选择,递增,增/减) 电源电压:2.5 V ~ 6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-WFDFN 裸露焊盘 供应商设备封装:8-TDFN(2x3) 包装:带卷 (TR) |

| AD5222BRZ1M | 功能描述:IC DGTL POT 128POS 1M DL 14SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数字电位器 系列:- 标准包装:3,300 系列:WiperLock™ 接片:257 电阻(欧姆):100k 电路数:1 温度系数:标准值 150 ppm/°C 存储器类型:易失 接口:3 线 SPI(芯片选择) 电源电压:1.8 V ~ 5.5 V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-VDFN 裸露焊盘 供应商设备封装:8-DFN-EP(3x3) 包装:带卷 (TR) |

| AD5222BRZ50 | 功能描述:IC POT DGTL DUAL 128POS 14SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数字电位器 系列:- 标准包装:3,300 系列:WiperLock™ 接片:257 电阻(欧姆):100k 电路数:1 温度系数:标准值 150 ppm/°C 存储器类型:易失 接口:3 线 SPI(芯片选择) 电源电压:1.8 V ~ 5.5 V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-VDFN 裸露焊盘 供应商设备封装:8-DFN-EP(3x3) 包装:带卷 (TR) |

| AD5227 | 制造商:AD 制造商全称:Analog Devices 功能描述:64-Position Up/Down Control Digital Potentiometer |

发布紧急采购,3分钟左右您将得到回复。