- 您现在的位置:买卖IC网 > PDF目录8718 > AD5313BRUZ-REEL (Analog Devices Inc)IC DAC 10BIT DUAL R-R 16-TSSOP PDF资料下载

参数资料

| 型号: | AD5313BRUZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/28页 |

| 文件大小: | 0K |

| 描述: | IC DAC 10BIT DUAL R-R 16-TSSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 2,500 |

| 设置时间: | 7µs |

| 位数: | 10 |

| 数据接口: | 串行 |

| 转换器数目: | 2 |

| 电压电源: | 单电源 |

| 功率耗散(最大): | 2.5mW |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 2 电压,单极;2 电压,双极 |

| 采样率(每秒): | 143k |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD5303/AD5313/AD5323

Rev. B | Page 17 of 28

SERIAL INTERFACE

The AD5303/AD5313/AD5323 are controlled over a versatile,

3-wire serial interface, which operates at clock rates up to

30 MHz and is compatible with SPI, QSPI, MICROWIRE,

and DSP interface standards.

INPUT SHIFT REGISTER

The input shift register is 16 bits wide. Data is loaded into

the device as a 16-bit word under the control of a serial clock

input, SCLK. The timing diagram for this operation is shown in

Figure 5. The 16-bit word consists of four control bits followed

by 8 /10 /12 bits of DAC data, depending on the device type.

The first bit loaded is the MSB (Bit 15), which determines whether

the data is for DAC A or DAC B. Bit 14 determines the output

range (0 V to VREF or 0 V to 2 VREF). Bit 13 and Bit 12 control the

operating mode of the DAC.

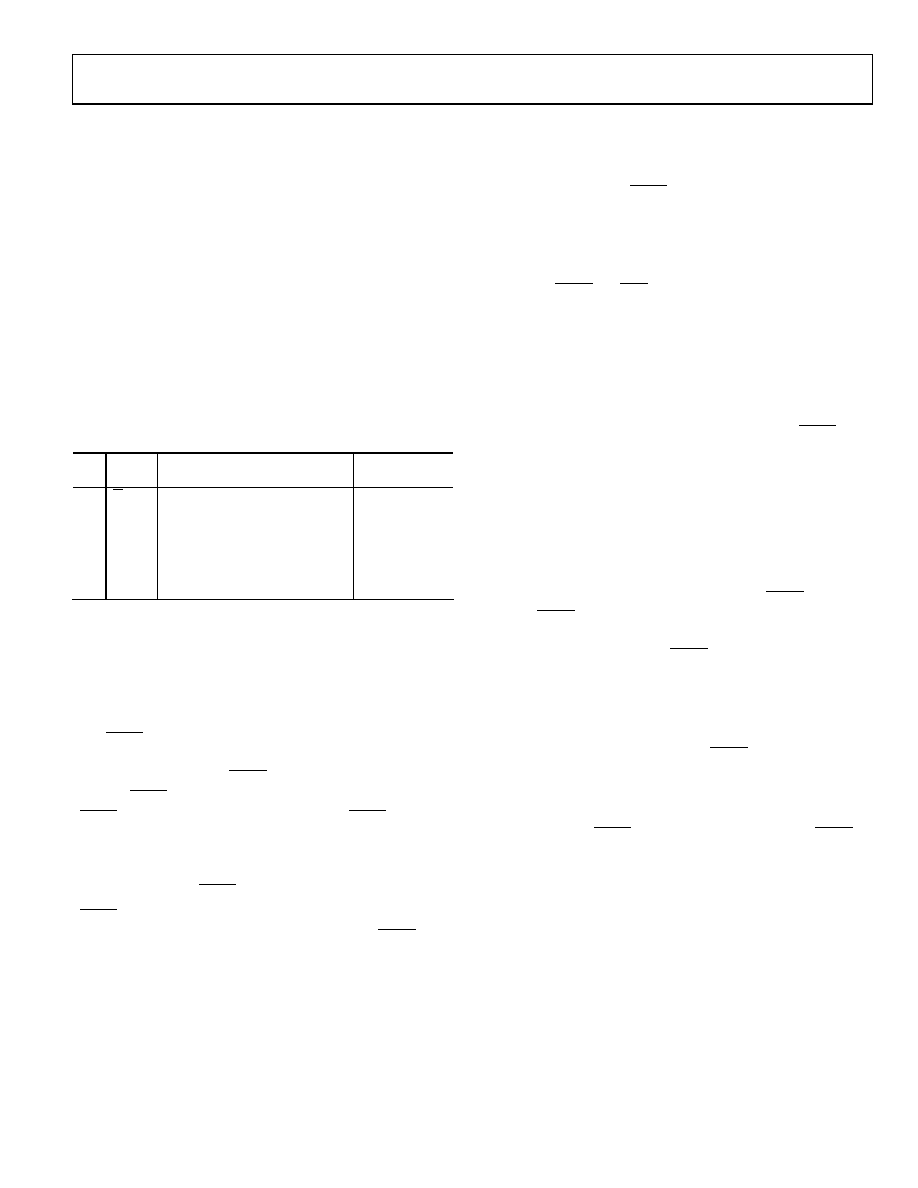

Table 6. Control Bits

Bit

Name

Function

Power-On

Default

15

A/B

0: data written to DAC A

1: data written to DAC B

N/A

14

GAIN

0: output range of 0 V to VREF

1: output range of 0 V to 2 VREF

0

13

PD1

Mode bit

0

12

PD0

Mode bit

0

The remaining bits are DAC data bits, starting with the MSB

and ending with the LSB. The AD5323 uses all 12 bits of DAC

data; the AD5313 uses 10 bits and ignores the 2 LSBs. The

AD5303 uses eight bits and ignores the last four bits. The data

format is straight binary, with all 0s corresponding to 0 V output,

and all 1s corresponding to full-scale output (VREF 1 LSB).

The SYNC input is a level-triggered input that acts as a frame

synchronization signal and chip enable. Data can be transferred

into the device only while SYNC is low. To start the serial data

transfer, SYNC should be taken low, observing the minimum

SYNC to SCLK rising edge setup time, t4. After SYNC goes low,

serial data is shifted into the device’s input shift register on the

falling edges of SCLK for 16 clock pulses. Any data and clock

pulses after the 16th are ignored, and no further serial data

transfer occurs until SYNC is taken high and low again.

SYNC may be taken high after the falling edge of the 16th SCLK

pulse, observing the minimum SCLK falling edge to SYNC

rising edge time, t7.

After the end of serial data transfer, data is automatically

transferred from the input shift register to the input register

of the selected DAC. If SYNC is taken high before the 16th

falling edge of SCLK, the data transfer is aborted and the input

registers are not updated.

When data has been transferred into both input registers, the

DAC registers of both DACs may be simultaneously updated,

by taking LDAC low. CLR is an active low, asynchronous clear

that clears the input and DAC registers of both DACs to all 0s.

LOW POWER SERIAL INTERFACE

To reduce the power consumption of the device even further,

the interface only powers up fully when the device is being

written to. As soon as the 16-bit control word has been written

to the part, the SCLK and DIN input buffers are powered down.

They only power up again following a falling edge of SYNC.

DOUBLE-BUFFERED INTERFACE

The DACs all have double-buffered interfaces consisting of two

banks of registers—input registers and DAC registers. The input

register is connected directly to the input shift register and the

digital code is transferred to the relevant input register on com-

pletion of a valid write sequence. The DAC register contains the

digital code used by the resistor string.

Access to the DAC register is controlled by the LDAC function.

When LDAC is high, the DAC register is latched and the input

register may change state without affecting the contents of the

DAC register. However, when LDAC is brought low, the DAC

register becomes transparent and the contents of the input reg-

ister are transferred to it.

This is useful if the user requires simultaneous updating of

both DAC outputs. The user may write to both input registers

individually and then, by pulsing the LDAC input low, both

outputs update simultaneously.

These parts contain an extra feature whereby the DAC register

is not updated unless its input register has been updated since

the last time that LDAC was brought low. Normally, when LDAC

is brought low, the DAC registers are filled with the contents of

the input registers. In the case of the AD5303/AD5313/AD5323,

the part only updates the DAC register if the input register has

been changed since the last time the DAC register was updated,

thereby removing unnecessary digital crosstalk.

相关PDF资料 |

PDF描述 |

|---|---|

| AD5304ARMZ | IC DAC 8BIT QUAD VOUT 10MSOP |

| ICS95V157AGLFT | IC CLK BUFF 1:10 233MHZ 48-TSSOP |

| VI-J61-MZ-F4 | CONVERTER MOD DC/DC 12V 25W |

| VI-J61-MZ-F3 | CONVERTER MOD DC/DC 12V 25W |

| VI-J61-MZ-F1 | CONVERTER MOD DC/DC 12V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5313BRUZ-REEL7 | 功能描述:IC DAC 10BIT DUAL R-R 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:LTC263x 12-, 10-, and 8-Bit VOUT DAC Family 特色产品:LTC2636 - Octal 12-/10-/8-Bit SPI VOUT DACs with 10ppm/°C Reference 标准包装:91 系列:- 设置时间:4µs 位数:10 数据接口:MICROWIRE?,串行,SPI? 转换器数目:8 电压电源:单电源 功率耗散(最大):2.7mW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-WFDFN 裸露焊盘 供应商设备封装:14-DFN-EP(4x3) 包装:管件 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD5313R | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual, 10-Bit nanoDAC with 2 ppm/C Reference, SPI Interface |

| AD5313RBCPZ-RL7 | 功能描述:数模转换器- DAC 10-Bit 2-CHSPI on-chip ref RoHS:否 制造商:Analog Devices 转换器数量:4 DAC 输出端数量:4 转换速率: 分辨率:12 bit 接口类型:Serial (I2C) 稳定时间: 最大工作温度:+ 105 C 安装风格: 封装 / 箱体:TSSOP 封装:Reel |

| AD5313RBRUZ | 功能描述:数模转换器- DAC 10-Bit 2-ch SPI nanoDAC+with on-chip ref RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| AD5313RBRUZ-RL7 | 功能描述:数模转换器- DAC 10-Bit 2-CHSPI on-chip ref RoHS:否 制造商:Analog Devices 转换器数量:4 DAC 输出端数量:4 转换速率: 分辨率:12 bit 接口类型:Serial (I2C) 稳定时间: 最大工作温度:+ 105 C 安装风格: 封装 / 箱体:TSSOP 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。