参数资料

| 型号: | AD5348BRUZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/24页 |

| 文件大小: | 0K |

| 描述: | IC DAC 12BIT OCTAL VOUT 38-TSSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 50 |

| 设置时间: | 8µs |

| 位数: | 12 |

| 数据接口: | 并联 |

| 转换器数目: | 8 |

| 电压电源: | 单电源 |

| 功率耗散(最大): | 8.3mW |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 38-TFSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 38-TSSOP |

| 包装: | 管件 |

| 输出数目和类型: | 8 电压,单极;8 电压,双极 |

| 采样率(每秒): | 125k |

| 产品目录页面: | 782 (CN2011-ZH PDF) |

AD5346/AD5347/AD5348

Rev. 0 | Page 17 of 24

PARALLEL INTERFACE

The AD5346/AD5347/AD5348 load their data as a single 8-,

10-, or 12-bit word.

Double-Buffered Interface

The AD5346/AD5347/AD5348 DACs all have double-buffered

interfaces consisting of an input register and a DAC register.

DAC data, BUF, and GAIN inputs are written to the input regis-

ter under control of the Chip Select (CS) and Write (WR) pins.

Access to the DAC register is controlled by the LDAC function.

When LDAC is high, the DAC register is latched and the input

register may change state without affecting the contents of the

DAC register. However, when LDAC is brought low, the DAC

register becomes transparent and the contents of the input

register are transferred to it. The gain and buffer control signals

are also double-buffered and are updated only when LDAC is

taken low.

This is useful if the user requires simultaneous updating of all

DACs and peripherals. The user can write to all input registers

individually and then, by pulsing the LDAC input low, all

outputs update simultaneously.

These parts contain an extra feature whereby the DAC register

is not updated unless its input register has been updated since

the last time that LDAC was brought low. Normally, when

LDAC is brought low, the DAC registers are filled with the

contents of the input registers. In the case of the AD5346/

AD5347/AD5348, the part updates the DAC register only if the

input register has been changed since the last time the DAC

register was updated. This removes unnecessary crosstalk.

Clear Input (CLR)

CLR is an active low, asynchronous clear that resets the input

and DAC registers.

Chip Select Input (CS)

CS is an active low input that selects the device.

Write Input (WR)

WR is an active low input that controls writing of data to the

device. Data is latched into the input register on the rising edge

of WR.

Read Input (RD)

RD is an active low input that controls when data is read back

from the internal DAC registers. On the falling edge of RD, data

is shifted onto the data bus. Under the conditions of a high

capacitive load and high supplies, the user must ensure that the

dynamic current remains at an acceptable level, therefore

ensuring that the die temperature is within specification. The

die temperature can be calculated as

TDIE

= TAMBIENT + VDD (IDD + IDYNAMIC)θJA

where IDYNAMIC =

cvf and

c = capacitance or the data bus

v = VDD

f = readback frequency

Load DAC Input (LDAC)

LDAC transfers data from the input register to the DAC register,

and therefore updates the outputs. The LDAC function enables

double-buffering of the DAC data, GAIN data, and BUF. There

are two LDAC modes:

Synchronous Mode.

In this mode, the DAC register is

updated after new data is read in on the rising edge of the

WR input. LDAC can be tied permanently low or pulsed as

shown in Figure 3.

Asynchronous Mode.

In this mode, the outputs are not

updated at the same time that the input register is written

to. When LDAC goes low, the DAC register is updated with

the contents of the input register.

POWER-ON RESET

The AD5346/AD5347/AD5348 have a power-on reset function,

so that they power up in a defined state. The power-on state is

Normal operation

Reference input buffered

0 V to VREF output range

Output voltage set to 0 V

Both input and DAC registers are filled with zeros and remain

so until a valid write sequence is made to the device. This is

particularly useful in applications where it is important to know

the state of the DAC outputs while the device is powering up.

POWER-DOWN MODE

The AD5346/AD5347/AD5348 have low power consumption,

dissipating typically 2.4 mW with a 3 V supply and 5 mW with

a 5 V supply. Power consumption can be further reduced when

the DACs are not in use by putting them into power-down

mode, which is selected by taking the PD pin low.

When the PD pin is high, the DACs work normally with a typi-

cal power consumption of 1 mA at 5 V (0.8 mA at 3 V). In

power-down mode, however, the supply current falls to 400 nA

at 5 V (120 nA at 3 V) when the DACs are powered down. Not

only does the supply current drop, but the output stage is also

internally switched from the output of the amplifier, making it

open-circuit. This has the advantage that the outputs are three-

state while the part is in power-down mode, and provides a

defined input condition for whatever is connected to the outputs

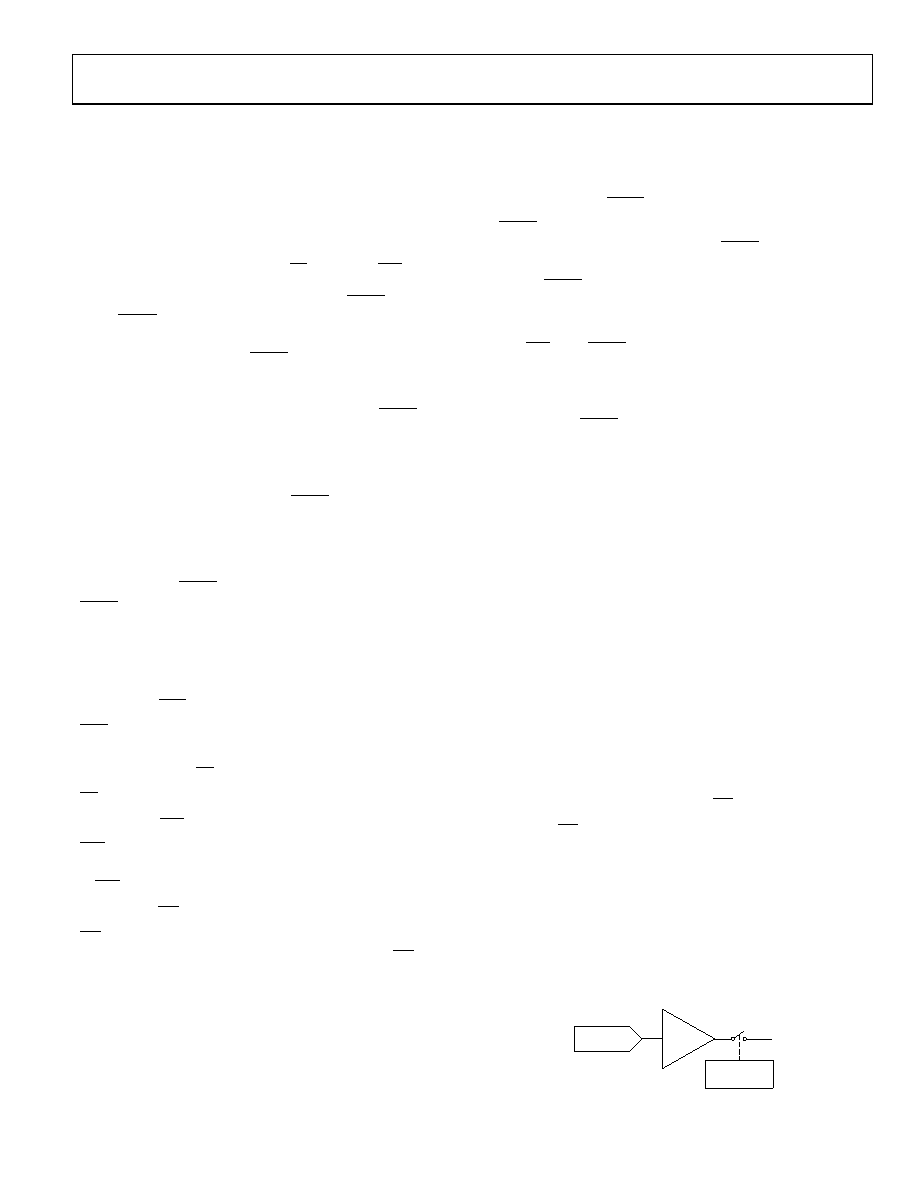

of the DAC amplifiers. The output stage is illustrated in Figure 39.

RESISTOR

STRING DAC

POWER-DOWN

CIRCUITRY

AMPLIFIER

VOUT

03331-0-022

Figure 39. Output Stage During Power-Down

相关PDF资料 |

PDF描述 |

|---|---|

| SI5338N-A-GM | IC CLK GEN I2C BUS PROG 24QFN |

| AD9761ARSZ | IC DAC 10BIT DUAL 40MSPS 28-SSOP |

| VI-J0R-MZ-F2 | CONVERTER MOD DC/DC 7.5V 25W |

| SI5338K-A-GM | IC CLK GEN I2C BUS PROG 24QFN |

| D38999/20KF32PC | CONN RCPT 32POS WALL MNT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5348BRUZRUZ | 制造商:Analog Devices 功能描述:DAC,AD5348B 12bit 8us octal TSSOP |

| AD534J | 制造商:AD 制造商全称:Analog Devices 功能描述:Internally Trimmed Precision IC Multiplier |

| AD534JD | 功能描述:IC TRIMMED MULTIPLIER/DIV 14-DIP RoHS:否 类别:集成电路 (IC) >> 线性 - 模拟乘法器,除法器 系列:- 标准包装:25 系列:HA 功能:模拟乘法器 位元/级数:四象限 封装/外壳:16-CDIP(0.300",7.62mm) 供应商设备封装:16-CDIP 侧面铜焊 包装:管件 |

| AD534JD/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog Multiplier/Divider |

| AD534JDZ | 功能描述:IC MULTIPLIER PREC TRIM 14-CDIP RoHS:是 类别:集成电路 (IC) >> 线性 - 模拟乘法器,除法器 系列:- 标准包装:25 系列:HA 功能:模拟乘法器 位元/级数:四象限 封装/外壳:16-CDIP(0.300",7.62mm) 供应商设备封装:16-CDIP 侧面铜焊 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。