- 您现在的位置:买卖IC网 > PDF目录8580 > AD5363BSTZ-REEL (Analog Devices Inc)IC DAC 14BIT 8CH SERIAL 52-LQFP PDF资料下载

参数资料

| 型号: | AD5363BSTZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/29页 |

| 文件大小: | 0K |

| 描述: | IC DAC 14BIT 8CH SERIAL 52-LQFP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 1,500 |

| 设置时间: | 20µs |

| 位数: | 14 |

| 数据接口: | 串行 |

| 转换器数目: | 8 |

| 电压电源: | 双 ± |

| 功率耗散(最大): | 209mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 52-LQFP |

| 供应商设备封装: | 52-LQFP(10x10) |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 8 电压,单极;8 电压,双极 |

| 采样率(每秒): | * |

| 配用: | EVAL-AD5363EBZ-ND - BOARD EVALUATION FOR AD5363 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

AD5362/AD5363

Rev. A | Page 16 of

28

THEORY OF OPERATION

DAC ARCHITECTURE

The AD5362/AD5363 contain eight DAC channels and eight

output amplifiers in a single package. The architecture of a

single DAC channel consists of a 16-bit (AD5362) or 14-bit

(AD5363) resistor-string DAC followed by an output buffer

amplifier. The resistor-string section is simply a string of resistors,

of equal value, from VREF0 or VREF1 to AGND. This type of

architecture guarantees DAC monotonicity. The 16-bit (AD5362)

or 14-bit (AD5363) binary digital code loaded to the DAC

register determines at which node on the string the voltage is

tapped off before being fed into the output amplifier. The output

amplifier multiplies the DAC output voltage by 4. The nominal

output span is 12 V with a 3 V reference and 20 V with a 5 V

reference.

CHANNEL GROUPS

The eight DAC channels of the AD5362/AD5363 are arranged

into two groups of four channels. The four DACs of Group 0

derive their reference voltage from VREF0. The four DACs of

Group 1 derive their reference voltage from VREF1. Each group

has its own signal ground pin.

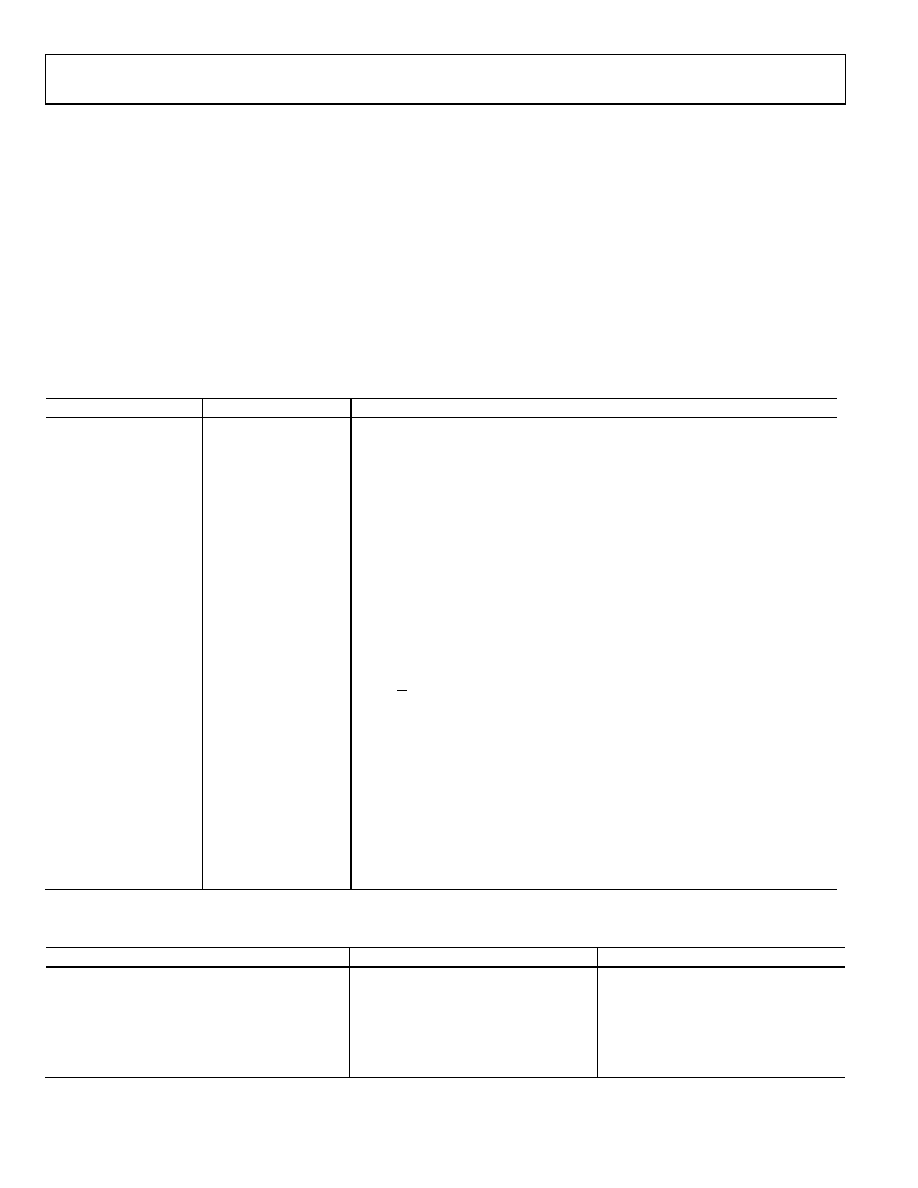

Table 7. AD5362/AD5363 Registers

Register Name

Word Length in Bits

Description

X1A (Group) (Channel)

16 (14)

Input Data Register A, one for each DAC channel.

X1B (Group) (Channel)

16 (14)

Input Data Register B, one for each DAC channel.

M (Group) (Channel)

16 (14)

Gain trim registers, one for each DAC channel.

C (Group) (Channel)

16 (14)

Offset trim registers, one for each DAC channel.

X2A (Group) (Channel)

16 (14)

Output Data Register A, one for each DAC channel. These registers store the final,

calibrated DAC data after gain and offset trimming. They are not readable or directly

writable.

X2B (Group) (Channel)

16 (14)

Output Data Register B, one for each DAC channel. These registers store the final,

calibrated DAC data after gain and offset trimming. They are not readable or directly

writable.

DAC (Group) (Channel)

Data registers from which the DACs take their final input data. The DAC registers are

updated from the X2A or X2B registers. They are not readable or directly writable.

OFS0

14

Offset DAC 0 data register: sets offset for Group 0.

OFS1

14

Offset DAC 1 data register: sets offset for Group 1.

Control

5

Bit 4 = overtemperature indicator.

Bit 3 = PEC error flag.

Bit 2 = A/B select.

Bit 1 = thermal shutdown.

Bit 0 = software power-down.

Monitor

6

Bit 5 = monitor enable.

Bit 4 = monitor DACs or monitor MON_INx pin.

Bit 3 to Bit 0 = monitor selection control.

GPIO

2

Bit 1 = GPIO configuration.

Bit 0 = GPIO data.

A/B Select 0

8

Bits [3:0] in this register determine whether a DAC in Group 0 takes its data from

Register X2A or Register X2B (0 = X2A, 1 = X2B).

A/B Select 1

8

Bits [3:0] in this register determine whether a DAC in Group 1 takes its data from

Register X2A or Register X2B (0 = X2A, 1 = X2B).

Table 8. AD5362/AD5363 Input Register Default Values

Register Name

AD5362 Default Value

AD5363 Default Value

X1A, X1B

0x8000

0x2000

M

0xFFFF

0x3FFF

C

0x8000

0x2000

OFS0, OFS1

0x2000

Control

0x00

A/B Select 0 and A/B Select 1

0x00

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B4Z-MX-B1 | CONVERTER MOD DC/DC 2V 30W |

| AD5363BCPZ-REEL7 | IC DAC 14BIT 8CH SERIAL 56-LFCSP |

| VI-B4Z-MW-B1 | CONVERTER MOD DC/DC 2V 40W |

| VI-B4Y-MY-B1 | CONVERTER MOD DC/DC 3.3V 33W |

| AD5765CSUZ-REEL7 | IC DAC 16BIT 5V QUAD 32-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5365D/BIN/883B | 制造商:Analog Devices 功能描述:- Rail/Tube |

| AD536A | 制造商:AD 制造商全称:Analog Devices 功能描述:Integrated Circuit True RMS-to-DC Converter |

| AD536AJC/D | 制造商:未知厂家 制造商全称:未知厂家 功能描述:RMS-to-DC Converter |

| AD536AJCHIPS | 制造商:AD 制造商全称:Analog Devices 功能描述:Integrated Circuit True RMS-to-DC Converter |

| AD536AJCWE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:RMS-to-DC Converter |

发布紧急采购,3分钟左右您将得到回复。