参数资料

| 型号: | AD5381BSTZ-5 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/40页 |

| 文件大小: | 0K |

| 描述: | IC DAC 12BIT 40CH 5V 100-LQFP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 产品变化通告: | AD5381,3 Redesign Change 24/Oct/2011 |

| 设计资源: | 40 Channels of Programmable Voltage with Excellent Temperature Drift Performance Using AD5381 (CN0010) AD5381 Channel Monitor Function (CN0013) |

| 标准包装: | 1 |

| 设置时间: | 6µs |

| 位数: | 12 |

| 数据接口: | 串行,并联 |

| 转换器数目: | 40 |

| 电压电源: | 单电源 |

| 功率耗散(最大): | 80mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-LQFP(14x14) |

| 包装: | 托盘 |

| 输出数目和类型: | 40 电压,单极 |

| 采样率(每秒): | 167k |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

Data Sheet

AD5381

Rev. D | Page 15 of 40

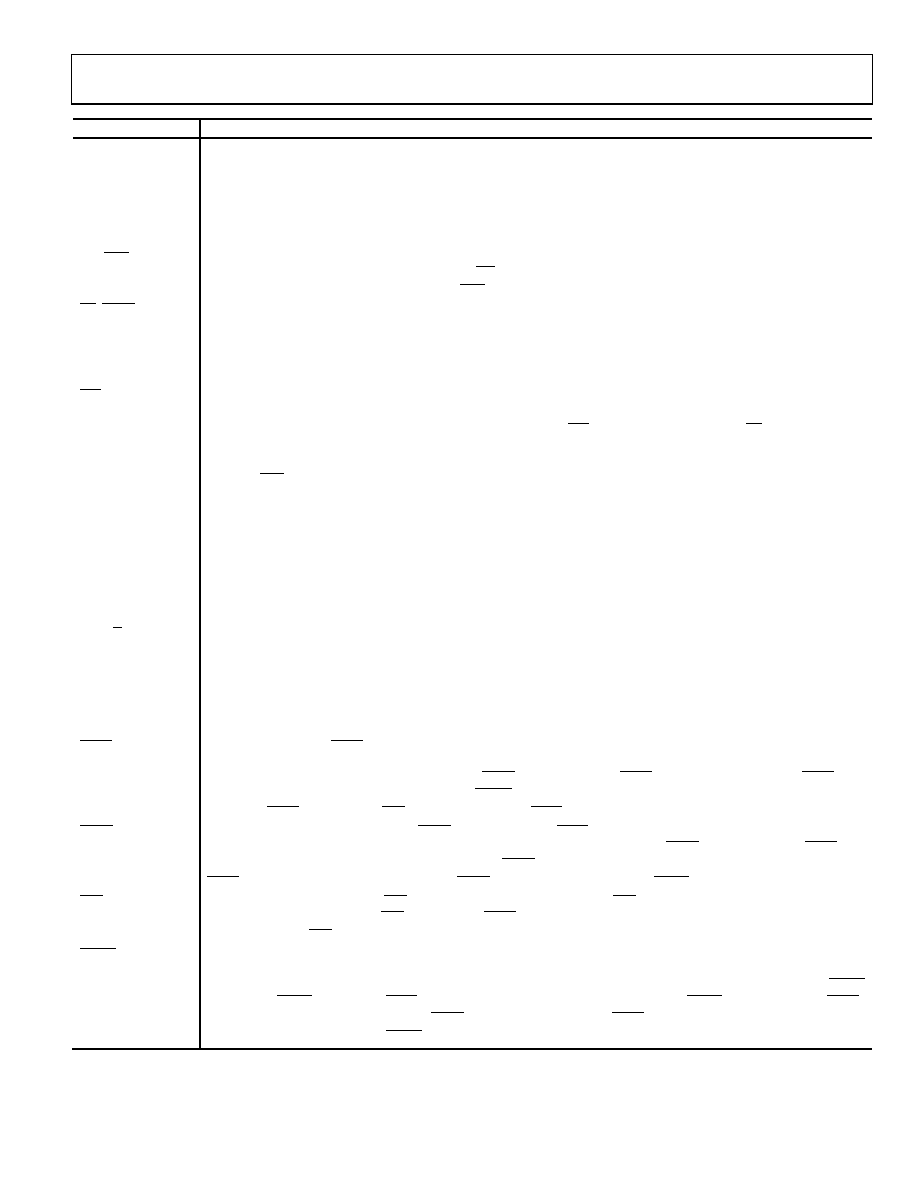

Mnemonic

Function

REFOUT/REFIN

The AD5381 contains a common REFOUT/REFIN pin. When the internal reference is selected, this pin is the reference

output. If the application requires an external reference, it can be applied to this pin and the internal reference can

be disabled via the control register. The default for this pin is a reference input.

VOUT39/MON_OUT

This pin has a dual function. It acts as a buffered output for Channel 39 in default mode. However, when the monitor

function is enabled, this pin acts as the output of a 39-to-1 channel multiplexer that can be programmed to

multiplex one of Channels 0 to 38 to the MON_OUT pin. The MON_OUT pin’s output impedance is typically 500

and is intended to drive a high input impedance like that exhibited by SAR ADC inputs.

SER/PAR

Interface Select Input. This pin allows the user to select whether the serial or parallel interface is used. If it is tied high,

the serial interface mode is selected and Pin 97 (SPI/I

2C) is used to determine if the interface mode is SPI or I2C.

Parallel interface mode is selected when SER/PAR is low.

CS/(SYNC/AD0)

In parallel interface mode, this pin acts as chip select input (level sensitive, active low). When low, the AD5381

is selected.

Serial Interface Mode. This is the frame synchronizationinput signal for the serialclock and data.

I2C Mode. This pin acts as a hardware address pin used in conjunction with AD1 to determine the software address

for the device on the I2C bus.

WR/(DCEN/AD1)

Multifunction Pin. In parallel interface mode, this pin acts as write enable. In serial interface mode, this pin acts as a

daisy-chain enable in SPI mode and as a hardware address pin in I2C mode.

Parallel Interface Write Input (edge sensitive). The rising edge of WR is used in conjunction with CS low,and the

address bus inputs to write to the selected device registers.

Serial Interface. Daisy-chain select input (level sensitive, active high). When high, this signal is used in conjunction

with SER/PAR high to enable the SPI serial interface daisy-chain mode.

I2C Mode. This pin acts as a hardware address pin used in conjunction with AD0 to determine the software address

for this device on the I2C bus.

DB11–DB0

Parallel Data Bus. DB11 is the MSB and DB0 is the LSB of the input data-word onthe AD5381.

A5–A0

Parallel Address Inputs. A5 to A0 are decoded to address one of the AD5381’s 40 input channels. Used in conjunction

with the REG1 and REG0 pins to determine the destination register for the input data.

REG1, REG0

In parallel interface mode, REG1 and REG0 are used in decoding the destination registers for the input data. REG1

and REG0 are decoded to address the input data register, offset register, or gain register for the selected channel and

are also used to decide the special function registers.

SDO/(A/B)

Serial Data Output in Serial Interface Mode. Three-stateable CMOS output. SDO can be used for daisy-chaining a

number of devices together. Data is clocked out on SDO on the rising edge of SCLK, and is valid on the fallingedge

of SCLK.

When operating in parallel interface mode, this pin acts as the A or B data register select when writing data to the

AD5381’s data registers with toggle mode selected (see the Toggle Mode Function section). In toggle mode, the

LDAC is used to switch the output between the data contained in the A and B data registers. All DAC channels

contain two data registers. In normal mode, Data Register A is the default for data transfers.

BUSY

Digital CMOS Output. BUSY goes low during internal calculations ofthe data (x2) loaded to the DAC data register.

During this time, the user can continue writing new data to the x1, c, and m registers, but no further updates to the

DAC registers and DAC outputs can take place. If LDAC is taken low while BUSY is low,this event is stored.BUSY also

goes low during power-on reset, and when the RESET pin is low.During this time,the interface is disabled andany

events on LDAC are ignored.A CLR operation also brings BUSYlow.

LDAC

Load DAC Logic Input (Active Low). If LDAC is taken low while BUSY is inactive (high),the contents of the input

registers are transferred to the DAC registers and the DAC outputs are updated. If LDAC is taken low while BUSYis

active and internal calculations are taking place, the LDAC event is stored and the DAC registers are updated when

BUSY goes inactive. However any events on LDAC during power-on reset or on RESET are ignored.

CLR

Asynchronous Clear Input. The CLR input is falling edge sensitive.When CLRis activated,all channels are updated

with the data contained in the CLR code register.BUSY is low for a duration of35 s while all channels are being

updated with the CLR code.

RESET

Asynchronous Digital Reset Input (Falling Edge Sensitive). The function of this pin is equivalent to that of the power-

on reset generator. When this pin is taken low, the state machine initiates a reset sequence to digitally reset the x1,

m, c, and x2 registers to their default power-on values. This sequence typically takes270 s. The falling edge of RESET

initiates the RESET process and BUSY goes low forthe duration,returning high when RESET is complete.While BUSY

is low, all interfaces are disabled and all LDAC pulses are ignored.When BUSYreturns high,the part resumes normal

operation and the status of the RESET pin is ignored untilthe next falling edge is detected.

相关PDF资料 |

PDF描述 |

|---|---|

| AD5382BSTZ-3 | IC DAC 14BIT 32CHAN 3V 100LQFP |

| AD5390BCPZ-5 | IC DAC 14BIT 16CHAN 5V 64LFCSP |

| AD5398ABCBZ-REEL | IC DAC 10BIT CURRENT-SINK 9WLCSP |

| AD5405YCPZ-REEL7 | IC DAC DUAL 12BIT MULT 40LFCSP |

| AD5415YRU | IC DAC DUAL 12BIT MULT 24-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5381BSTZ-5-REEL | 功能描述:IC DAC 12BIT 40CH 5V 100-LQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD5382BST-3 | 制造商:Analog Devices 功能描述:DAC 32-CH Resistor-String 14-bit 100-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:32/40-CHANNEL 3V/5V SINGLE SUPPLY 12/14-BIT VOUT DAC - Bulk |

| AD5382BST-3-REEL | 制造商:Analog Devices 功能描述:DAC 32-CH Resistor-String 14-bit 100-Pin LQFP T/R |

| AD5382BST-5 | 制造商:Analog Devices 功能描述:DAC 32-CH Resistor-String 14-bit 100-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:32-CHN 5V SINGLE SUPPLY 14-BIT VOUT I.C. - Bulk |

| AD5382BST-5-REEL | 制造商:Analog Devices 功能描述:DAC 32-CH Resistor-String 14-bit 100-Pin LQFP T/R |

发布紧急采购,3分钟左右您将得到回复。