- 您现在的位置:买卖IC网 > PDF目录8696 > AD5449YRUZ-REEL7 (Analog Devices Inc)IC DAC DUAL 12BIT MULT 16TSSOP PDF资料下载

参数资料

| 型号: | AD5449YRUZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/29页 |

| 文件大小: | 0K |

| 描述: | IC DAC DUAL 12BIT MULT 16TSSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 1,000 |

| 设置时间: | 80ns |

| 位数: | 12 |

| 数据接口: | 串行 |

| 转换器数目: | 2 |

| 电压电源: | 单电源 |

| 功率耗散(最大): | 3.5µW |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 4 电流,单极;4 电流,双极 |

| 采样率(每秒): | 2.47M |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

Data Sheet

AD5429/AD5439/AD5449

Rev. E | Page 15 of 28

THEORY OF OPERATION

DIGITAL-TO-ANALOG CONVERTER

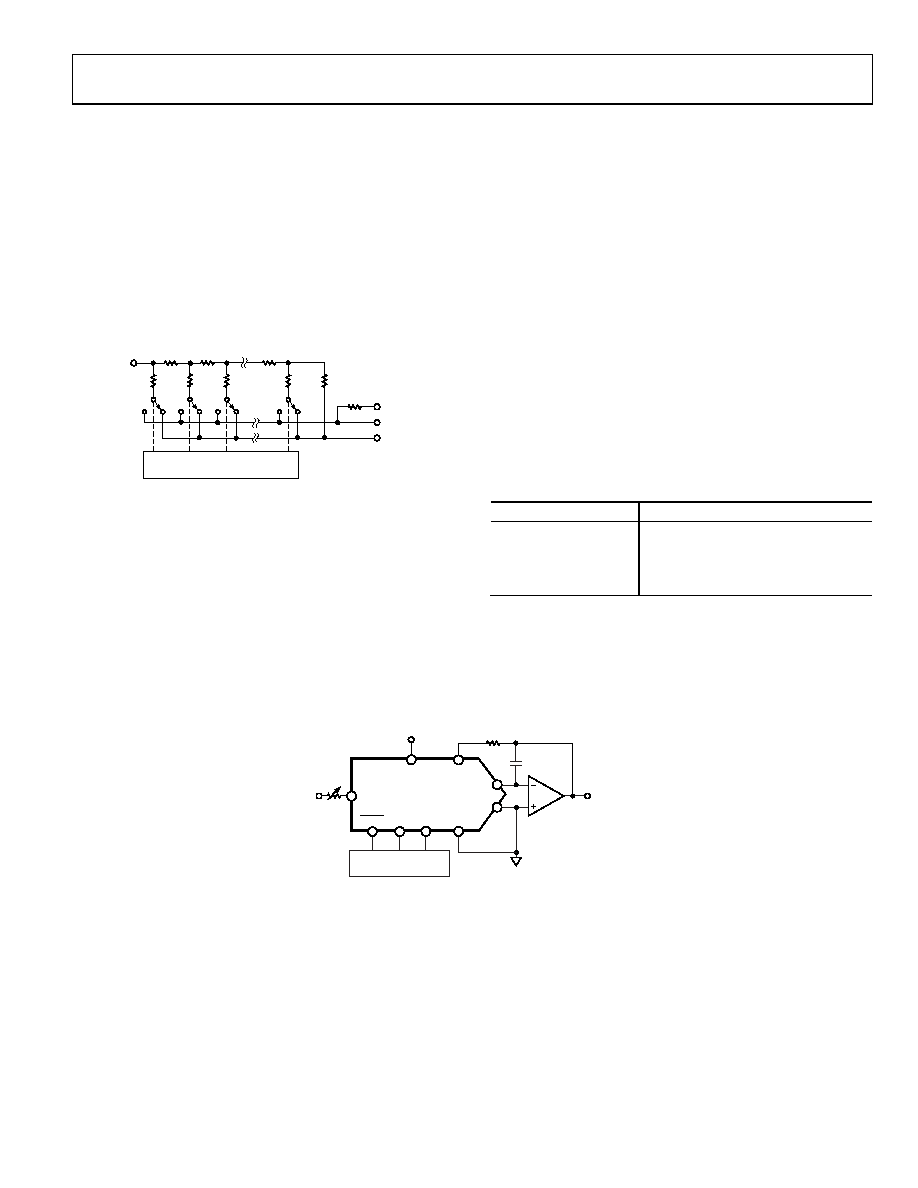

The AD5429/AD5439/AD5449 are 8-, 10-, and 12-bit, dual-

channel, current output DACs consisting of a standard inverting

R-2R ladder configuration. Figure 37 shows a simplified diagram

for a single channel of the AD5449. The feedback resistor, RFBA,

has a value of R. The value of R is typically 10 kΩ (with a

minimum of 8 kΩ and a maximum of 12 kΩ). If IOUT1A and

IOUT2A are kept at the same potential, a constant current flows

into each ladder leg, regardless of digital input code. Therefore,

the input resistance presented at VREFA is always constant.

2R

S1

2R

S2

2R

S3

2R

S12

2R

DAC DATA LATCHES

AND DRIVERS

R

RFBA

IOUT1A

IOUT2A

VREFA

04464-006

RR

R

Figure 37. Simplified Ladder

Access is provided to the VREFx, RFBx, IOUT1x, and IOUT2x termi-

nals of the DACs, making the devices extremely versatile and

allowing them to be configured in several operating modes, such

as unipolar mode, bipolar output mode, or single-supply mode.

CIRCUIT OPERATION

Unipolar Mode

Using a single op amp, these devices can easily be configured to

provide 2-quadrant multiplying operation or a unipolar output

voltage swing, as shown in Figure 38.

When an output amplifier is connected in unipolar mode, the

output voltage is given by

n

REF

OUT

D

V

2

/

where:

D

is the fractional representation of the digital word loaded to

the DAC.

D

= 0 to 255 (AD5429)

= 0 to 1023 (AD5439)

= 0 to 4095 (AD5449)

n

is the number of bits.

With a fixed 10 V reference, the circuit shown in Figure 38 gives

a unipolar 0 V to 10 V output voltage swing. When VIN is an ac

signal, the circuit performs 2-quadrant multiplication.

Table 5 shows the relationship between digital code and the

expected output voltage for unipolar operation using the 8-bit

AD5429 DAC.

Table 5. Unipolar Code Table

Digital Input

Analog Output (V)

1111 1111

VREF (255/256)

1000 0000

VREF (128/256) = VREF/2

0000 0001

VREF (1/256)

0000 0000

VREF (0/256) = 0

AD5429/

AD5439/

AD5449

04

46

4-

0

07

NOTES

1. R1 AND R2 USED ONLY IF GAIN ADJUSTMENT IS REQUIRED.

2. C1 PHASE COMPENSATION (1pF TO 2pF) MAY BE REQUIRED

3. DAC B OMITTED FOR CLARITY.

IOUT1A

IOUT2A

VREFx

VDD

C1

A1

VOUT = 0V TO –VREF

AGND

R2

VDD

VREF

SDIN

GND

SCLK

SYNC

RFBA

R1

IF A1 IS A HIGH SPEED AMPLIFIER.

MICROCONTROLLER

Figure 38. Unipolar Operation

相关PDF资料 |

PDF描述 |

|---|---|

| V300A8H400BF3 | CONVERTER MOD DC/DC 8V 400W |

| ICS8344AY-01LFT | IC CLOCK BUFFER MUX 2:24 48-LQFP |

| AD5447YRUZ-REEL | IC DAC 12BIT DUAL MULT 24TSSOP |

| ICS8536AG-02LFT | IC CLOCK BUFFER MUX 3:6 24-TSSOP |

| VI-B6W-MV-F4 | CONVERTER MOD DC/DC 5.5V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD544JH | 制造商:Rochester Electronics LLC 功能描述:ULTRA-LOW DRIFT OP AMP IC - Bulk |

| AD544JH/+ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD544KH | 制造商:AD 功能描述:544 ANALOG |

| AD544KH/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Operational Amplifier |

| AD544LH | 制造商:Rochester Electronics LLC 功能描述:ULTRA-LOW DRIFT OP AMP IC - Bulk |

发布紧急采购,3分钟左右您将得到回复。