- 您现在的位置:买卖IC网 > PDF目录8674 > AD5453YRM-REEL (Analog Devices Inc)IC DAC 14BIT MULTIPLYING 8-MSOP PDF资料下载

参数资料

| 型号: | AD5453YRM-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/28页 |

| 文件大小: | 0K |

| 描述: | IC DAC 14BIT MULTIPLYING 8-MSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 设计资源: | Unipolar, Precision DC Digital-to-Analog Conversion using AD5450/1/2/3 8-14-Bit DACs (CN0052) Precision, Bipolar, Configuration for AD5450/1/2/3 8-14bit Multiplying DACs (CN0053) AC Signal Processing Using AD5450/1/2/3 Current Output DACs (CN0054) Programmable Gain Element Using AD5450/1/2/3 Current Output DAC Family (CN0055) |

| 标准包装: | 3,000 |

| 位数: | 14 |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP,8-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 8-MSOP |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 1 电流,单极;1 电流,双极 |

| 采样率(每秒): | 2.7M |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD5450/AD5451/AD5452/AD5453

Data Sheet

Rev. G | Page 22 of 28

04

58

7-

0

5

10

0

00

0

11

0

CONTROL BITS

DATA BITS

10

0

00

0

00

11

0

CONTROL BITS

ACTUAL DATA FRAME

INTENDED DATA FRAME

DATA BITS

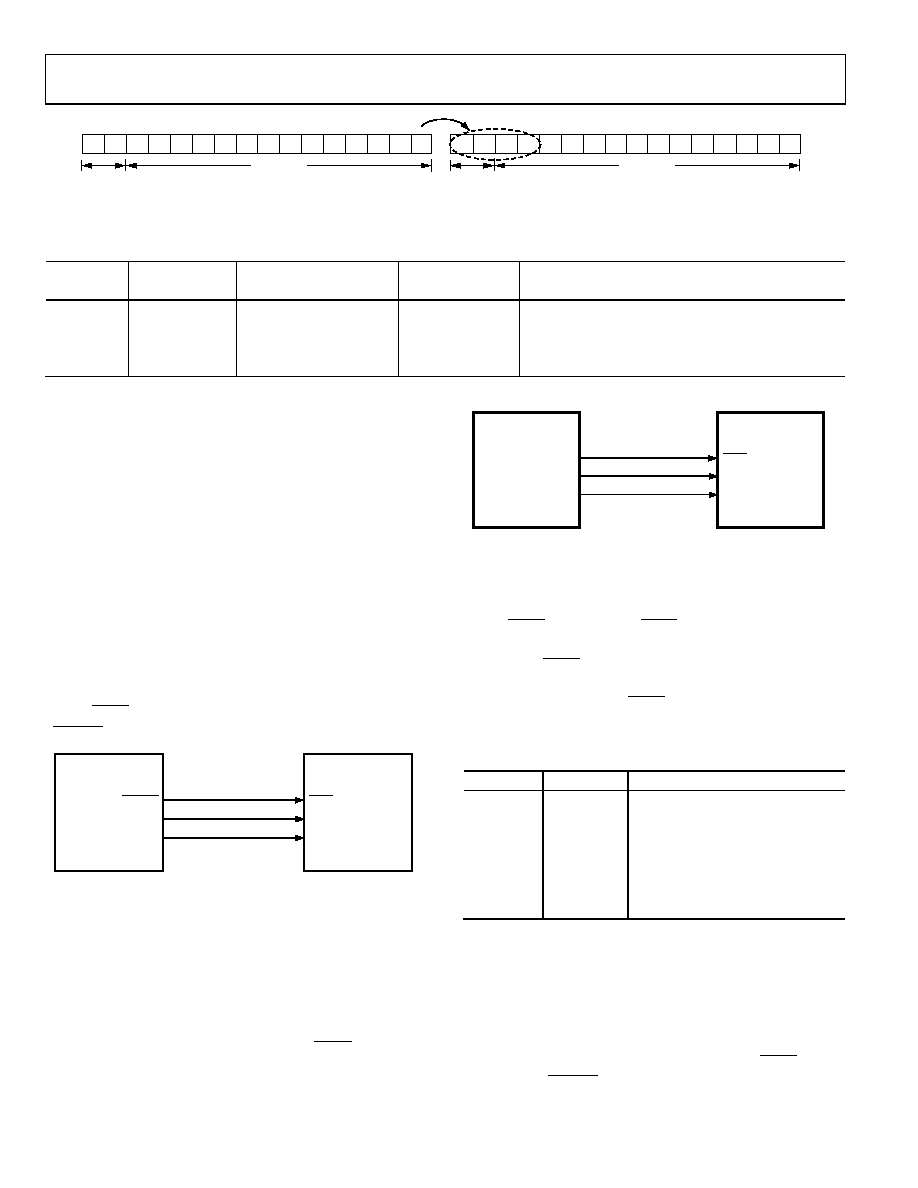

Figure 55. AD5453 Second Write, Incomplete Data Sequence (0x3200) and Subsequent Additional Bits (0xF200)

Table 11.

Writing

Sequence

Data Write in

Shift Register

Action Expected

Data Transfer to

the Device

Action Carried Out

1

0x3FFF

Load and update 0x3FFF

0x3FFF

Load and update 0x3FFF

2

0x3200

Load and update 0x3200

0xF200

Clock data to shift register upon rising edge (0xF200)

MICROPROCESSOR INTERFACING

/AD5453 DAC is through a serial bus that uses standard protocol

and is compatible with microcontrollers and DSP processors.

The communication channel is a 3-wire interface consisting of

a clock signal, a data signal, and a synchronization signal. The

the default being data valid upon the falling edge of SCLK, but

this is changeable using the control bits in the data-word.

ADSP-21xx-to-AD5450/AD5451/AD5452/AD5453

Interface

The ADSP-21xx family of DSPs is easily interfaced to a AD5450/

logic. Figure 56 is an example of an SPI interface between the DAC

and the ADSP-2191M. SCK of the DSP drives the serial data line,

SDIN. SYNC is driven from one of the port lines, in this case

SPIxSEL.

SCLK

SCK

SYNC

SPIxSEL

SDIN

MOSI

ADSP-2191M*

*ADDITIONAL PINS OMITTED FOR CLARITY

AD5450/AD5451/

AD5452/AD5453*

0

458

7-

1

00

A serial interface between the DAC and DSP SPORT is shown

in Figure 57. In this example, SPORT0 is used to transfer data to

the DAC shift register. Transmission is initiated by writing a

word to the Tx register after the SPORT has been enabled. In a

write sequence, data is clocked out upon each rising edge of the

DSP’s serial clock and clocked into the DAC input shift register

upon the falling edge of its SCLK. The update of the DAC

output takes place upon the rising edge of the SYNC signal.

SCLK

SYNC

TFS

SDIN

DT

ADSP-2101/

ADSP-2191M*

*ADDITIONAL PINS OMITTED FOR CLARITY

0

4587-

051

AD5450/AD5451/

AD5452/AD5453*

Figure 57. ADSP-2101/ADSP-2191M-

Communication between two devices at a given clock speed is

possible when the following specifications are compatible:

frame SYNC delay and frame SYNC setup-and-hold, data delay

and data setup-and-hold, and SCLK width. The DAC interface

expects a t4 (SYNC falling edge to SCLK falling edge setup time)

of 13 ns minimum. See the ADSP-21xx User Manual for infor-

mation on clock and frame SYNC frequencies for the SPORT

register. Table 12 shows the setup for the SPORT control register.

Table 12. SPORT Control Register Setup

Name

Setting

Description

TFSW

1

Alternate framing

INVTFS

1

Active low frame signal

DTYPE

00

Right justify data

ISCLK

1

Internal serial clock

TFSR

1

Frame every word

ITFS

1

Internal framing signal

SLEN

1111

16-bit data-word

ADSP-BF5xx-to-AD5450/AD5451/AD5452/AD5453

Interface

The ADSP-BF5xx family of processors has an SPI-compatible

port that enables the processor to communicate with SPI-

compatible devices. A serial interface between the BlackFin

shown in Figure 58. In this configuration, data is transferred

through the MOSI (master output, slave input) pin. SYNC is

driven by the SPIxSEL pin, which is a reconfigured

programmable flag pin.

相关PDF资料 |

PDF描述 |

|---|---|

| SY100H641LJC | IC CLK BUFFER 1:9 135MHZ 28-PLCC |

| AD9760ARUZRL7 | IC DAC 10BIT 125MSPS 28TSSOP |

| SY100H641JC TR | IC CLK BUFFER 1:9 135MHZ 28-PLCC |

| SY100H641JC | IC CLK BUFFER 1:9 135MHZ 28-PLCC |

| SY100H641AJC | IC CLK BUFFER 1:9 80MHZ 28-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5453YRM-REEL7 | 功能描述:IC DAC 14BIT MULTIPLYING 8-MSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

| AD5453YRMZ | 功能描述:IC DAC 14BIT MULTIPLYING 8-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 设置时间:4µs 位数:12 数据接口:串行 转换器数目:2 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-uMAX 包装:管件 输出数目和类型:2 电压,单极 采样率(每秒):* 产品目录页面:1398 (CN2011-ZH PDF) |

| AD5453YRMZ-REEL | 功能描述:IC DAC 14BIT MULTIPLYING 8-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:LTC263x 12-, 10-, and 8-Bit VOUT DAC Family 特色产品:LTC2636 - Octal 12-/10-/8-Bit SPI VOUT DACs with 10ppm/°C Reference 标准包装:91 系列:- 设置时间:4µs 位数:10 数据接口:MICROWIRE?,串行,SPI? 转换器数目:8 电压电源:单电源 功率耗散(最大):2.7mW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-WFDFN 裸露焊盘 供应商设备封装:14-DFN-EP(4x3) 包装:管件 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD5453YRMZ-REEL7 | 功能描述:IC DAC 14BIT MULTIPLYING 8-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 设置时间:4µs 位数:12 数据接口:串行 转换器数目:2 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-uMAX 包装:管件 输出数目和类型:2 电压,单极 采样率(每秒):* 产品目录页面:1398 (CN2011-ZH PDF) |

| AD5453YUJ | 制造商:AD 制造商全称:Analog Devices 功能描述:8/10/12/14-Bit High Bandwidth Multiplying DACs with Serial Interface |

发布紧急采购,3分钟左右您将得到回复。