参数资料

| 型号: | AD5532HSABCZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/12页 |

| 文件大小: | 0K |

| 描述: | IC DAC 14BIT 32CH HS 74-CSPBGA |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 1 |

| 设置时间: | 10µs |

| 位数: | 14 |

| 数据接口: | 串行 |

| 转换器数目: | 34 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 623mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 74-LBGA,CSPBGA |

| 供应商设备封装: | 74-CSPBGA(12x12) |

| 包装: | 托盘 |

| 输出数目和类型: | 32 电压,单极 |

| 采样率(每秒): | 1.1M |

| 配用: | EVAL-AD5532HSEBZ-ND - BOARD EVAL FOR AD5532HS EVAL-AD5532EBZ-ND - BOARD EVAL FOR AD5532 |

REV. 0

AD5532HS

–6–

PIN FUNCTION DESCRIPTIONS

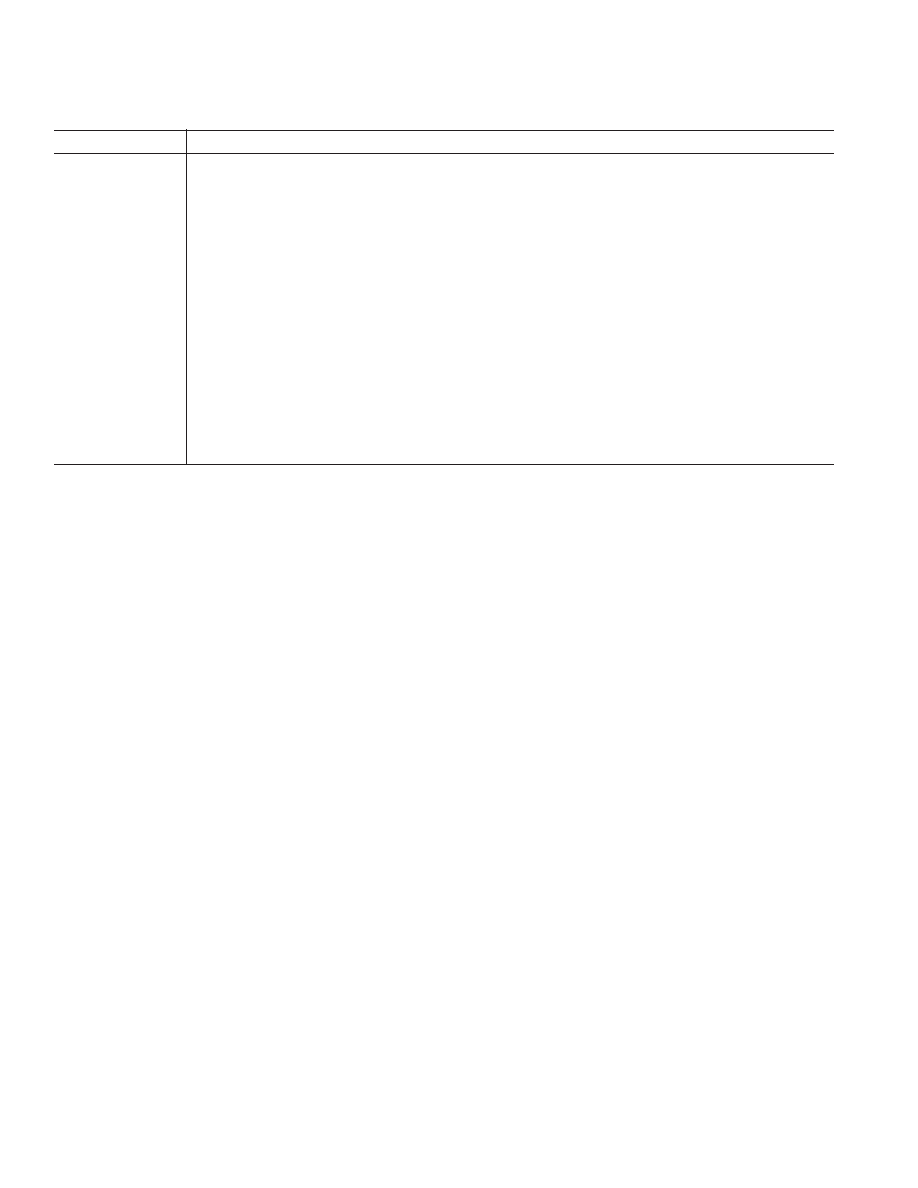

Pin

Function

AGND (1–2)

Analog GND Pins.

AVCC (1–2)

Analog Supply Pins. Voltage range from 4.75 V to 5.25 V.

VDD (1–4)

VDD Supply Pins. Voltage range from 8 V to 12 V.

VSS (1–4)

VSS Supply Pins. Voltage range from –4.75 V to –12 V.

DGND

Digital GND Pins.

DVCC

Digital Supply Pins. Voltage range from 2.7 V to 5.25 V.

DAC_GND (1–2)

Reference GND Supply for All the DACs.

REF_IN

Reference Voltage for Channels 0–31.

VOUT0–VOUT31

Analog Output Voltages from the 32 Channels.

SYNC

Active Low Input. This is the Frame Synchronization signal for the serial interface. While SYNC is low,

data is transferred in on the falling edge of SCLK.

SCLK

*

Serial Clock Input. Data is clocked into the shift register on the falling edge of SCLK. This

operates at clock speeds up to 30 MHz.

DIN*

Serial Data Input. Data must be valid on the falling edge of SCLK.

OFFS_IN

Offset Input. The user can connect this to GND or REF_IN to determine the output span.

RESET*

Active Low Input. This pin can also be used to reset the complete device to its power-on-reset conditions.

*Internal pull-up device on this logic input. Therefore, it can be left floating and will default to a logic high condition.

TERMINOLOGY

Integral Nonlinearity (INL)

A measure of the maximum deviation from a straight line pass-

ing through the endpoints of the DAC transfer function. It is

expressed as a percentage of full-scale range.

Differential Nonlinearity (DNL)

The difference between the measured change and the ideal 1 LSB

change between any two adjacent codes. A specified DNL of

±1 LSB maximum ensures monotonicity.

Offset Error

A measure of the error present at the device output with all 0s

loaded to the DAC. It includes the offset of the DAC and the

output amplifier. It is expressed in mV.

Full-Scale Error

A measure of the output error with all 1s loaded to the DAC.

Ideally the output should be 2 REF_IN if OFFS_IN = 0. It is

expressed as a percentage of full-scale range.

DC Power-Supply Rejection Ratio (PSRR)

A measure of the change in analog output for a change in supply

voltage (VDD and VSS). It is expressed in dB. VDD and VSS are

varied

±5%.

DC Crosstalk

The dc change in the output level of one DAC at midscale in

response to a full-scale code change (all 0s to all 1s and vice

versa) and output change of all other DACs. It is expressed in

V.

Output Temperature Coefficient

A measure of the change in analog output with changes in tem-

perature. It is expressed in ppm/

°C.

Output Voltage Settling Time

The time taken from when the last data bit is clocked into the

DAC until the output has settled to within

± 0.5 LSB of its

final value.

Digital-to-Analog Glitch Impulse

The area of the glitch injected into the analog output when

the code in the DAC register changes state. It is specified as

the area of the glitch in nV-secs when the digital code is changed

by 1 LSB at the major carry transition (011 . . . 11 to 100 . . . 00

or 100 . . . 00 to 011 . . . 11).

Digital Crosstalk

The glitch impulse transferred to the output of one DAC at

midscale while a full-scale code change (all 1s to all 0s and vice

versa) is being written to another DAC. It is expressed in nV-secs.

Analog Crosstalk

The area of the glitch transferred to the output (VOUT) of one

DAC due to a full-scale change in the output (VOUT) of another

DAC. The area of the glitch is expressed in nV-secs.

Digital Feedthrough

A measure of the impulse injected into the analog outputs from the

digital control inputs when the part is not being written to, i.e.,

SYNC is high. It is specified in nV-secs and measured with a

worst-case change on the digital input pins, e.g., from all 0s

to all 1s and vice versa.

Output Noise Spectral Density

A measure of internally generated random noise. Random noise is

characterized as a spectral density (voltage per root Hertz). It is

measured by loading all DACs to midscale and measuring

noise at the output. It is measured in nV/

√Hz.

相关PDF资料 |

PDF描述 |

|---|---|

| AD5532ABCZ-5 | IC DAC 14BIT 32CH BIPO 74-CSPBGA |

| VI-B4L-MU-S | CONVERTER MOD DC/DC 28V 200W |

| VE-JT1-MW-S | CONVERTER MOD DC/DC 12V 100W |

| AD5532ABCZ-2 | IC DAC 14BIT 32CH BIPO 74-CSPBGA |

| VE-J53-MW-S | CONVERTER MOD DC/DC 24V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5533 | 制造商:AD 制造商全称:Analog Devices 功能描述:32-Channel Infinite Sample-and-Hold |

| AD5533ABC-1 | 制造商:Analog Devices 功能描述:Sample and Hold 32-CH 16us 74-Pin CSP-BGA |

| AD5533ABC-1REEL | 制造商:Analog Devices 功能描述:Sample and Hold 32-CH 16us 74-Pin CSP-BGA T/R |

| AD5533ABCZ-1 | 制造商:Analog Devices 功能描述:Sample and Hold 32-CH 16us 74-Pin CSP-BGA |

| AD5533B | 制造商:AD 制造商全称:Analog Devices 功能描述:32-Channel Precision Infinite Sample-and-Hold |

发布紧急采购,3分钟左右您将得到回复。