- 您现在的位置:买卖IC网 > PDF目录10524 > AD574AJPZ (Analog Devices Inc)IC ADC 12BIT W/REF/CLK 28-PLCC PDF资料下载

参数资料

| 型号: | AD574AJPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/12页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT W/REF/CLK 28-PLCC |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 28.6k |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 725mW |

| 电压电源: | 双 ± |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-LCC(J 形引线) |

| 供应商设备封装: | 28-PLCC(11.51x11.51) |

| 包装: | 管件 |

| 输入数目和类型: | 2 个单端,单极;2 个单端,双极 |

AD574A

REV. B

–11–

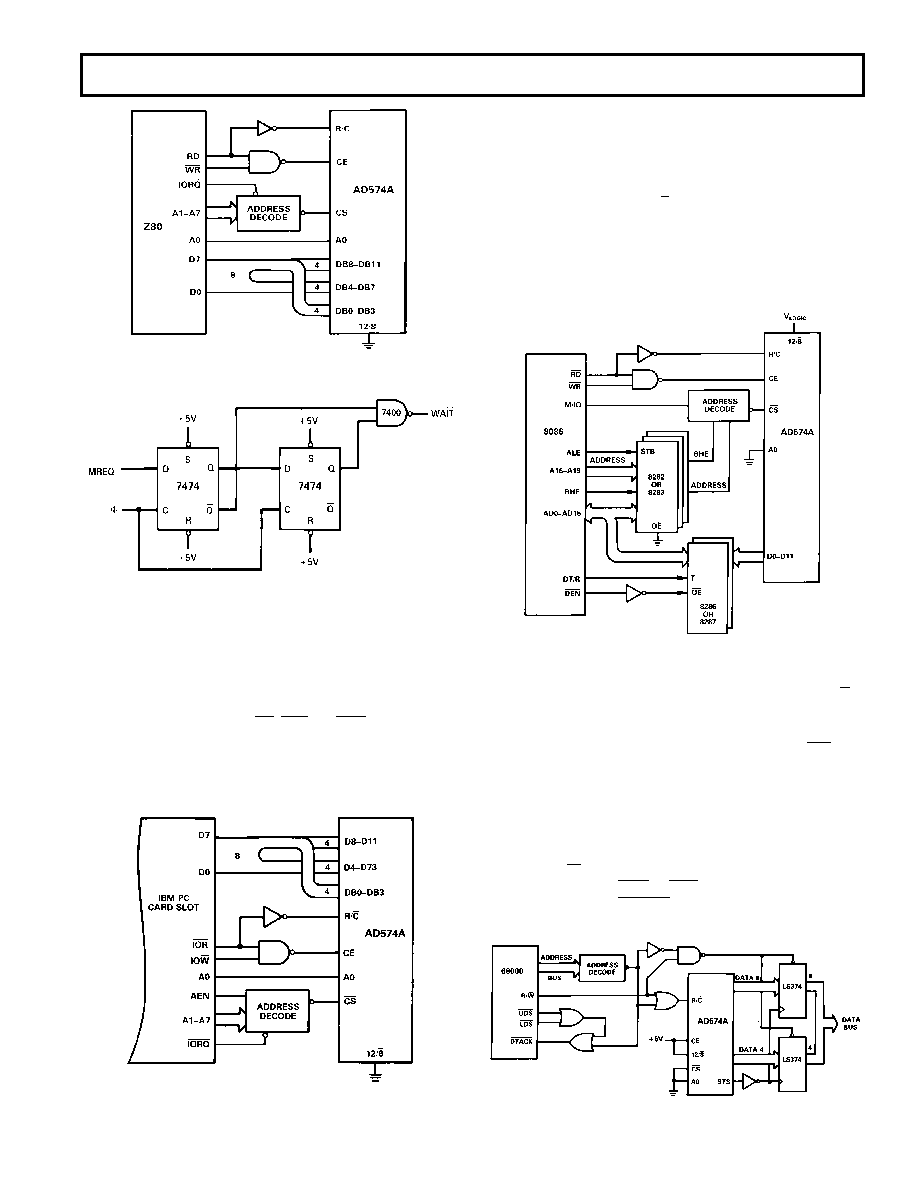

Figure 15. Z80—AD574A Interface

Figure 16. Wait State Generator

IBM PC Interface

The AD574A appears in Figure 17 interfaced to the 4 MHz

8088 processor of an IBM PC. Since the device resides in I/O

space, its address is decoded from only the lower ten address

lines and must be gated with AEN (active low) to mask out in-

ternal DMA cycles which use the same I/O address space. This

active low signal is applied to CS. IOR and IOW are used to

initiate the conversion and read, and are gated together to drive

the chip enable, CE. Because the data bus width is limited to

8 bits, the AD574A data resides in two adjacent addresses

selected by A0.

Figure 17. IBM PC—AD574A Interface

Note: Due to the large number of options that may be installed

in the PC, the I/O bus loading should be limited to one Schottky

TTL load. Therefore, a buffer/driver should be used when inter-

facing more than two AD574As to the I/O bus.

8086 Interface

The data mode select pin (12/8) of the AD574A should be con-

nected to VLOGIC to provide a 12-bit data output. To prevent

possible bus contention, a demultiplexed and buffered address/

data bus is recommended. In the cases where the 8-bit short

conversion cycle is not used, A0 should be tied to digital com-

mon. Figure 18 shows a typical 8086 configuration.

Figure 18. 8086—AD574A with Buffered Bus lnterface

For clock speeds greater than 4 MHz wait state insertion similar

to Figure 16 is recommended to ensure sufficient CE and R/C

pulse duration.

The AD574A can also be interfaced in a stand-alone mode (see

Figure 13). A low going pulse derived from the 8086’s WR sig-

nal logically ORed with a low address decode starts the conver-

sion. At the end of the conversion, STS clocks the data into the

three-state latches.

68000 Interface

The AD574, when configured in the stand-alone mode, will eas-

ily interface to the 4 MHz version of the 68000 microprocessor.

The 68000 R/W signal combined with a low address decode ini-

tiates conversion. The UDS or LDS signal, with the decoded

address, generates the DTACK input to the processor, latching

in the AD574A’s data. Figure 19 illustrates this configuration.

Figure 19. 68000—AD574A Interface

相关PDF资料 |

PDF描述 |

|---|---|

| VE-2T1-IW-F4 | CONVERTER MOD DC/DC 12V 100W |

| VE-2T1-IW-F3 | CONVERTER MOD DC/DC 12V 100W |

| VE-244-IW-F4 | CONVERTER MOD DC/DC 48V 100W |

| AD9248BCPZ-40 | IC ADC 14BIT DUAL 40MSPS 64LFCSP |

| SSM2305RMZ-REEL7 | IC AMP AUDIO 2.8W MONO D 8MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD574AJPZ-REEL | 功能描述:IC ADC 12BIT W/REF/CLK 28-PLCC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD574AJX | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 12-Bit A/D Converter |

| AD574AK | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 12-Bit A/D Converter |

| AD574AKD | 功能描述:IC ADC 12BIT W/REF 28-CDIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD574AKD/+ | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。