参数资料

| 型号: | AD633JR |

| 厂商: | Analog Devices Inc |

| 文件页数: | 21/21页 |

| 文件大小: | 0K |

| 描述: | IC ANALOG MULTIPLIER 8-SOIC |

| 标准包装: | 98 |

| 功能: | 模拟乘法器 |

| 位元/级数: | 四象限 |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SO |

| 包装: | 管件 |

AD633

Data Sheet

Rev. J | Page 8 of 20

FUNCTIONAL DESCRIPTION

The AD633 is a low cost multiplier comprising a translinear

core, a buried Zener reference, and a unity-gain connected

output amplifier with an accessible summing node. Figure 1

shows the functional block diagram. The differential X and Y

inputs are converted to differential currents by voltage-to-

current converters. The product of these currents is generated

by the multiplying core. A buried Zener reference provides an

overall scale factor of 10 V. The sum of (X × Y)/10 + Z is then

applied to the output amplifier. The amplifier summing node Z

allows the user to add two or more multiplier outputs, convert

the output voltage to a current, and configure various analog

computational functions.

Inspection of the block diagram shows the overall transfer

function is

(

)(

)

Z

V

Y2

Y1

X2

X1

W

+

=

10

(1)

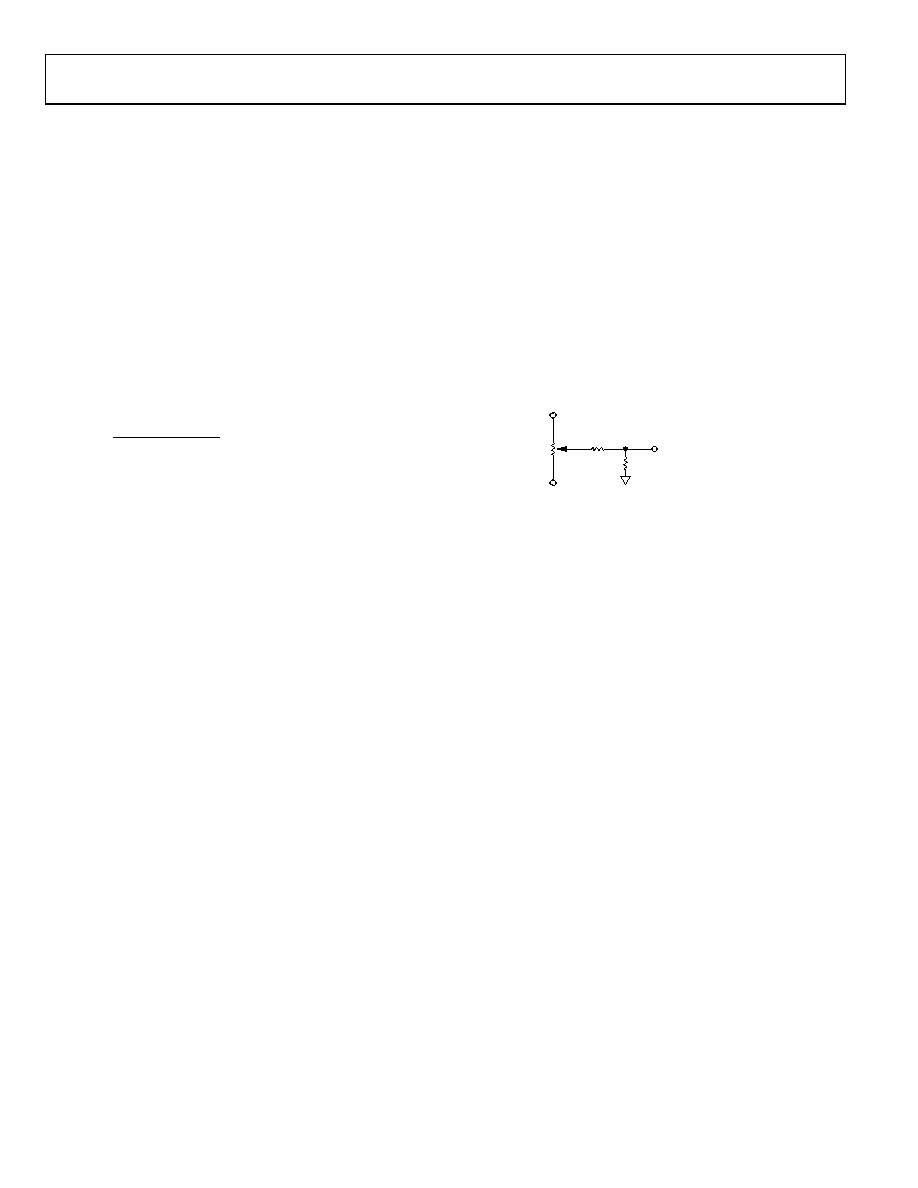

ERROR SOURCES

Multiplier errors consist primarily of input and output offsets,

scale factor error, and nonlinearity in the multiplying core. The

input and output offsets can be eliminated by using the optional

trim of Figure 11. This scheme reduces the net error to scale

factor errors (gain error) and an irreducible nonlinearity

component in the multiplying core. The X and Y nonlinearities

are typically 0.4% and 0.1% of full scale, respectively. Scale

factor error is typically 0.25% of full scale. The high impedance

Z input should always reference the ground point of the driven

system, particularly if it is remote. Likewise, the differential X

and Y inputs should reference their respective grounds to

realize the full accuracy of the AD633.

±50mV

TO APPROPRIATE

INPUT TERMINAL

(FOR EXAMPLE, X2, Y2, Z)

50k

1k

300k

+VS

–VS

00786-

010

Figure 11. Optional Offset Trim Configuration

相关PDF资料 |

PDF描述 |

|---|---|

| AD7148ACPZ-1REEL | IC CAP-TO-DGTL CONV PROG 16LFCSP |

| AD734BQ | IC MULTIPLIER 4-QUADRANT 14-CDIP |

| AD790SQ | IC COMPARATOR PREC W/LATCH 8CDIP |

| AD8013ANZ | IC OPAMP SINGLE 14DIP |

| AD8023ARZ | IC AMP VIDEO TRIPLE HC 14-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD633JR | 制造商:Analog Devices 功能描述:SEMICONDUCTORSLINEAR |

| AD633JR-REEL | 功能描述:IC MULTIPLIER ANALOG 8-SOIC T/R RoHS:否 类别:集成电路 (IC) >> 线性 - 模拟乘法器,除法器 系列:- 标准包装:25 系列:HA 功能:模拟乘法器 位元/级数:四象限 封装/外壳:16-CDIP(0.300",7.62mm) 供应商设备封装:16-CDIP 侧面铜焊 包装:管件 |

| AD633JR-REEL7 | 功能描述:IC MULTIPLIER ANALOG 8-SOIC T/R RoHS:否 类别:集成电路 (IC) >> 线性 - 模拟乘法器,除法器 系列:- 标准包装:25 系列:HA 功能:模拟乘法器 位元/级数:四象限 封装/外壳:16-CDIP(0.300",7.62mm) 供应商设备封装:16-CDIP 侧面铜焊 包装:管件 |

| AD633JRZ | 功能描述:IC MULTIPLIER ANALOG 8-SOIC RoHS:是 类别:集成电路 (IC) >> 线性 - 模拟乘法器,除法器 系列:- 标准包装:25 系列:HA 功能:模拟乘法器 位元/级数:四象限 封装/外壳:16-CDIP(0.300",7.62mm) 供应商设备封装:16-CDIP 侧面铜焊 包装:管件 |

| AD633JRZ-R7 | 功能描述:IC MULTIPLIER ANALOG 8SOIC RoHS:是 类别:集成电路 (IC) >> 线性 - 模拟乘法器,除法器 系列:- 标准包装:25 系列:HA 功能:模拟乘法器 位元/级数:四象限 封装/外壳:16-CDIP(0.300",7.62mm) 供应商设备封装:16-CDIP 侧面铜焊 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。