- 您现在的位置:买卖IC网 > PDF目录10030 > AD6654CBC (Analog Devices Inc)IC ADC 14BIT W/4CH RSP 256CSPBGA PDF资料下载

参数资料

| 型号: | AD6654CBC |

| 厂商: | Analog Devices Inc |

| 文件页数: | 2/88页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT W/4CH RSP 256CSPBGA |

| 标准包装: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 92.16M |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 2.5W |

| 电压电源: | 模拟和数字 |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BGA,CSPBGA |

| 供应商设备封装: | 256-CSPBGA(17x17) |

| 包装: | 托盘 |

| 输入数目和类型: | 1 个差分,单极 |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

AD6654

Rev. 0 | Page 10 of 88

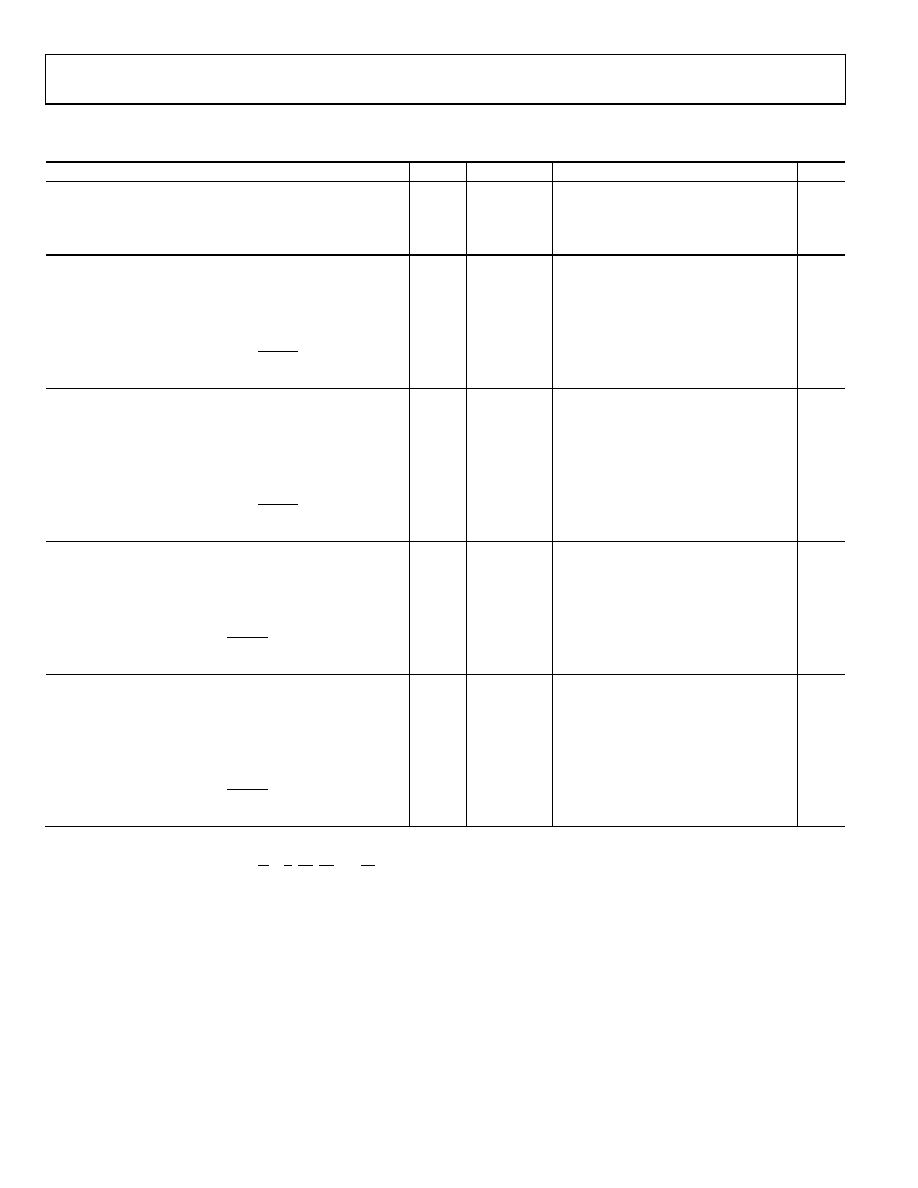

MICROPORT TIMING CHARACTERISTICS

Table 8.

Temp

Test Level

Min

Typ

Max

Unit

MICROPORT CLOCK TIMING REQUIREMENTS

tCPUCLK

CPUCLK Period

Full

IV

10.0

ns

tCPUCLKL

CPUCLK Low Time

Full

IV

1.53

0.5 × tCPUCLK

ns

tCPUCLKH

CPUCLK High Time

Full

IV

1.70

0.5 × tCPUCLK

ns

INM MODE WRITE TIMING (MODE = 0)

tSC

Control3 to

↑CPUCLK Setup Time

Full

IV

0.80

ns

tHC

Control3 to

↑CPUCLK Hold Time

Full

IV

0.09

ns

tSAM

Address/Data to

↑CPUCLK Setup Time

Full

IV

0.76

ns

tHAM

Address/Data to

↑CPUCLK Hold Time

Full

IV

0.20

ns

tDRDY

↑CPUCLK to RDY (DTACK) Delay

Full

IV

3.51

6.72

ns

tACC

Write Access Time

Full

IV

3 × tCPUCLK

9 × tCPUCLK

ns

INM MODE READ TIMING (MODE = 0)

tSC

Control3 to

↑CPUCLK Setup Time

Full

IV

1.00

ns

tHC

Control3 to

↑CPUCLK Hold Time

Full

IV

0.03

ns

tSAM

Address to

↑CPUCLK Setup Time

Full

IV

0.80

ns

tHAM

Address to

↑CPUCLK Hold Time

Full

IV

0.20

ns

tDD

↑CPUCLK to Data Delay

Full

V

5.0

ns

tDRDY

↑CPUCLK to RDY (DTACK) Delay

Full

IV

4.50

6.72

ns

tACC

Read Access Time

Full

IV

3 × tCPUCLK

9 × tCPUCLK

ns

MNM MODE WRITE TIMING (MODE = 1)

tSC

Control3 to

↑CPUCLK Setup Time

Full

IV

1.00

ns

tHC

Control3 to

↑CPUCLK Hold Time

Full

IV

0.00

ns

tSAM

Address/Data to

↑CPUCLK Setup Time

Full

IV

0.00

ns

tHAM

Address/Data to

↑CPUCLK Hold Time

Full

IV

0.57

ns

tDDTACK

↑CPUCLK to DTACK (RDY) Delay

Full

IV

4.10

5.72

ns

tACC

Write Access Time

Full

IV

3 × tCPUCLK

9 × tCPUCLK

ns

MNM MODE READ TIMING (MODE = 1)

tSC

Control3 to

↑CPUCLK Setup Time

Full

IV

1.00

ns

tHC

Control3 to

↑CPUCLK Hold Time

Full

IV

0.00

ns

tSAM

Address to

↑CPUCLK Setup Time

Full

IV

0.00

ns

tHAM

Address to

↑CPUCLK Hold Time

Full

IV

0.57

ns

tDD

CPUCLK to Data Delay

Full

V

5.0

ns

tDDTACK

↑CPUCLK to DTACK (RDY) Delay

Full

IV

4.20

6.03

ns

tACC

Read Access Time

Full

IV

3 × tCPUCLK

9 × tCPUCLK

ns

1 All timing specifications are valid over the VDDCORE range of 1.7 V to 1.9 V, and the VDDIO range of 3.0 V to 3.6 V.

2 CLOAD = 40 pF on all outputs, unless otherwise noted.

3 Specification pertains to control signals: R/W, (WR), DS, (RD), and CS.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-26R-MX-F4 | CONVERTER MOD DC/DC 7.5V 75W |

| LTC1348IG#TRPBF | IC TXRX 3.3V/5V RS232 28-SSOP |

| AD1555AP | IC ADC PGA 24BIT LN 28PLCC |

| AD9639BCPZRL-170 | IC ADC 12B 170MSPS QUAD 72LFCSP |

| SP332ET-L/TR | IC TXRX RS232/485 SRL 28WSOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6654CBCZ | 功能描述:IC ADC 14BIT W/4CH RSP 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654XBCZ | 制造商:Analog Devices 功能描述:14-BIT, 92.16 MSPS, 4 & 6-CHANNEL WIDEBAND IF TO BASE BAND R - Bulk |

| AD6655 | 制造商:AD 制造商全称:Analog Devices 功能描述:IF Diversity Receiver |

| AD6655-125EBZ | 功能描述:BOARD EVAL W/AD6655 & SOFTWARE RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:- 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796 |

| AD6655-125EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:IF Diversity Receiver |

发布紧急采购,3分钟左右您将得到回复。