参数资料

| 型号: | AD667JPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/8页 |

| 文件大小: | 0K |

| 描述: | IC DAC 12BIT W/BUFF LATCH 28PLCC |

| 标准包装: | 39 |

| 设置时间: | 3µs |

| 位数: | 12 |

| 转换器数目: | 1 |

| 电压电源: | 双 ± |

| 功率耗散(最大): | 1W |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-LCC(J 形引线) |

| 供应商设备封装: | 28-PLCC(11.51x11.51) |

| 包装: | 管件 |

| 输出数目和类型: | * |

| 采样率(每秒): | 500k |

AD667

REV. A

–6–

Small resistors may be added to the feedback resistors in order

to accomplish small modifications in the scaling. For example, if

a 10.24 V full scale is desired, a 140

1% low TC metal-film

resistor can be added in series with the internal (nominal) 5k

feedback resistor, and the gain trim potentiometer (between

Pins 6 and 7) should be increased to 200

. In the bipolar

mode, increase the value of the bipolar offset trim potentiometer

also to 200

.

GROUNDING RULES

The AD667 brings out separate analog and power grounds to

allow optimum connections for low noise and high speed perfor-

mance. These grounds should be tied together at one point,

usually the device power ground. The separate ground returns

are provided to minimize current flow in low level signal paths.

The analog ground at Pin 5 is the ground point for the output

amplifier and is thus the “high quality” ground for the AD667;

it should be connected directly to the analog reference point of

the system. The power ground at Pin 16 can be connected to

the most convenient ground point; analog power return is

preferred. If power ground contains high frequency noise be-

yond 200 mV, this noise may feed through the converter, thus

some caution will be required in applying these grounds.

It is also important to apply decoupling capacitors properly on

the power supplies for the AD667 and the output amplifier. The

correct method for decoupling is to connect a capacitor from

each power supply pin of the AD667 to the analog ground pin

of the AD667. Any load driven by the output amplifier should

also be referred to the analog ground pin.

OPTIMIZING SETTLING TIME

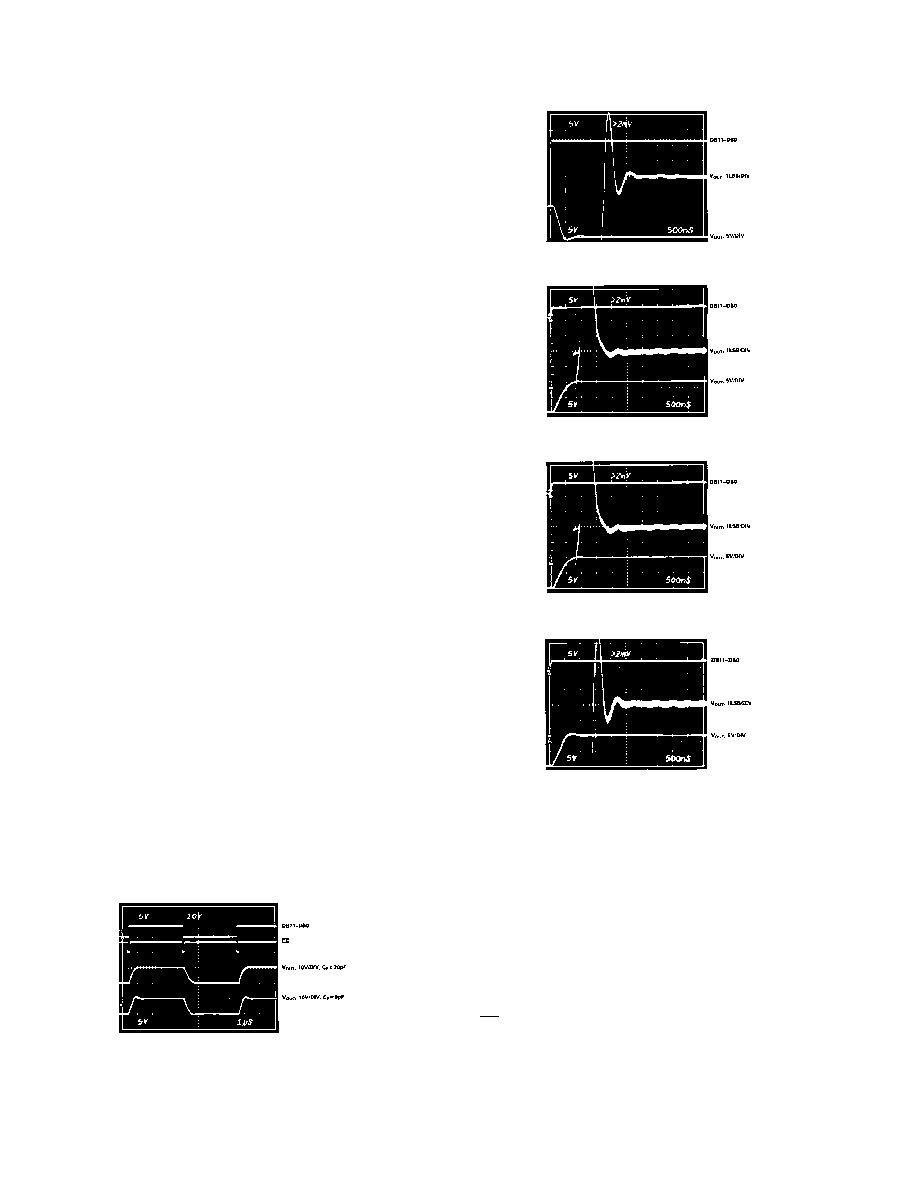

The dynamic performance of the AD667’s output amplifier can

be optimized by adding a small (20 pF) capacitor across the

feedback resistor. Figure 4 shows the improvement in both

large-signal and small-signal settling for the 10 V range. In Fig-

ure 4a, the top trace shows the data inputs (DB11–DB0 tied to-

gether), the second trace shows the CS pulse (A3–A0 tied low),

and the lower two traces show the analog outputs for CF = 0 pF

and 20 pF respectively.

Figures 4b and 4c show the settling time for the transition from

all bits on to all bits off. Note that the settling time to

±1/2 LSB

for the 10 V step is improved from 2.4 microseconds to 1.6 mi-

croseconds by the addition of the 20 pF capacitor.

Figures 4d and 4e show the settling time for the transition from

all bits off to all bits on. The improvement in settling time

gained by adding CC = 20 pF is similar.

a. Large Scale Settling

b. Fine-Scale Settling, CF = 0 pF

c. Fine-Scale Settling, CF = 20 pF

d. Fine-Scale Settling, CF = 0 pF

e. Fine-Scale Settling, CF = 20 pF

Figure 4. Settling Time Performance

DIGITAL CIRCUIT DETAILS

The bus interface logic of the AD667 consists of four indepen-

dently addressable registers in two ranks. The first rank consists

of three four-bit registers which can be loaded directly from a

4-, 8-, 12-, or 16-bit microprocessor bus. Once the complete

12-bit data word has been assembled in the first rank, it can be

loaded into the 12-bit register of the second rank. This

double-buffered organization avoids the generation of spurious

analog output values. Figure 5 shows the block diagram of the

AD667 logic section.

The latches are controlled by the address inputs, A0–A3, and

the CS input. All control inputs are active low, consistent with

general practice in microprocessor systems. The four address

lines each enable one of the four latches, as indicated in Table II.

All latches in the AD667 are level-triggered. This means that

data present during the time when the control signals are valid

will enter the latch. When any one of the control signals returns

high, the data is latched.

相关PDF资料 |

PDF描述 |

|---|---|

| AD667JP | IC DAC 12BIT V-OUT 28-PLCC |

| VI-2TF-IV-F2 | CONVERTER MOD DC/DC 72V 150W |

| 74AHCT1G04GV,125 | IC INVERTER SC74A-5 |

| LTC2610IUFD#PBF | IC DAC OCTAL R-R 14BIT 20-QFN |

| LTC2600IGN#TRPBF | IC DAC OCTAL R-R 16BIT 16SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD667JPZ-REEL | 功能描述:IC DAC 12BIT W/BUFF LATCH 28PLCC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD667KN | 功能描述:IC DAC 12BIT W/BUFF LATCH 28-DIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:2,400 系列:- 设置时间:- 位数:18 数据接口:串行 转换器数目:3 电压电源:模拟和数字 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:36-TFBGA 供应商设备封装:36-TFBGA 包装:带卷 (TR) 输出数目和类型:* 采样率(每秒):* |

| AD667KN/+ | 制造商:Analog Devices 功能描述:DAC 1CH CURRENT STEERING 12-BIT 28PDIP W - Rail/Tube 制造商:Rochester Electronics LLC 功能描述:IC - 12-BIT A/D CONVERTER - Bulk |

| AD667KNZ | 功能描述:IC DAC 12BIT W/BUFF LATCH 28-DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD667KP | 功能描述:IC DAC 12BIT W/BUFF LATCH 28PLCC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

发布紧急采购,3分钟左右您将得到回复。