- 您现在的位置:买卖IC网 > PDF目录17025 > AD677-EB (Analog Devices Inc)BOARD EVAL SAMPLING ADC AD677 PDF资料下载

参数资料

| 型号: | AD677-EB |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/16页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL SAMPLING ADC AD677 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 100k |

| 数据接口: | 串行 |

| 输入范围: | ±VREF |

| 在以下条件下的电源(标准): | 450mW @ 100kSPS |

| 工作温度: | 0°C ~ 70°C |

| 已用 IC / 零件: | AD677 |

| 已供物品: | 板 |

| 相关产品: | AD677KNZ-ND - IC ADC 16BIT SAMPLING 16DIP AD677JNZ-ND - IC ADC 16BIT SAMPLING 16-DIP AD677KRZ-REEL-ND - IC ADC 16BIT 100KSPS 28-SOIC AD677KRZ-ND - IC ADC 16BIT 100KSPS 28-SOIC AD677JRZ-REEL-ND - IC ADC 16BIT 100KSPS 28-SOIC TR AD677JRZ-ND - IC ADC 16BIT SAMPLING 28-SOIC AD677KR-REEL-ND - IC ADC 16BIT SAMPLING 28-SOIC AD677KN-ND - IC ADC 16BIT SAMPLING 16-DIP AD677KD-ND - IC ADC 16BIT SAMPLING 16-DIP AD677JR-REEL-ND - IC ADC 16BIT SAMPLING 28-SOIC 更多... |

AD677

REV. A

–4–

(TMIN to TMAX, VCC = +12 V

5%, VEE = –12 V

5%, VDD = +5 V

10%)

1

TIMING SPECIFICATIONS

Parameter

Symbol

Min

Typ

Max

Units

Conversion Period

2, 3

tC

10

1000

s

CLK Period

4

tCLK

480

ns

Calibration Time

tCT

85532

tCLK

Sampling Time

tS

2

s

Last CLK to SAMPLE Delay

5

tLCS

2.1

s

SAMPLE Low

tSL

100

ns

SAMPLE to Busy Delay

tSS

30

75

ns

1st CLK Delay

tFCD

50

ns

CLK Low

6

tCL

50

ns

CLK High

6

tCH

50

ns

CLK to BUSY Delay

tCB

180

300

ns

CLK to SDATA Valid

tCD

50

100

175

ns

CLK to SCLK High

tCSH

100

180

300

ns

SCLK Low

tSCL

50

80

ns

SDATA to SCLK High

tDSH

50

80

ns

CAL High Time

tCALH

50

ns

CAL to BUSY Delay

tCALB

15

50

ns

NOTES

1See the “CONVERSION CONTROL” and “AUTOCALIBRATION” sections for detailed explanations of the above timing.

2Depends upon external clock frequency; includes acquisition time and conversion time. The maximum conversion period is specified to account for the droop of the

internal sample/hold function. Operation at slower rates may degrade performance.

3t

C = tFCD + 16

× t

CLK + tLCS.

4580 ns is recommended for optimal accuracy over temperature (not necessary during calibration cycle).

5If SAMPLE goes high before the 17th CLK pulse, the device will start sampling approximately 100 ns after the rising edge of the 17th CLK pulse.

6t

CH + tCL = tCLK and must be greater than 480 ns.

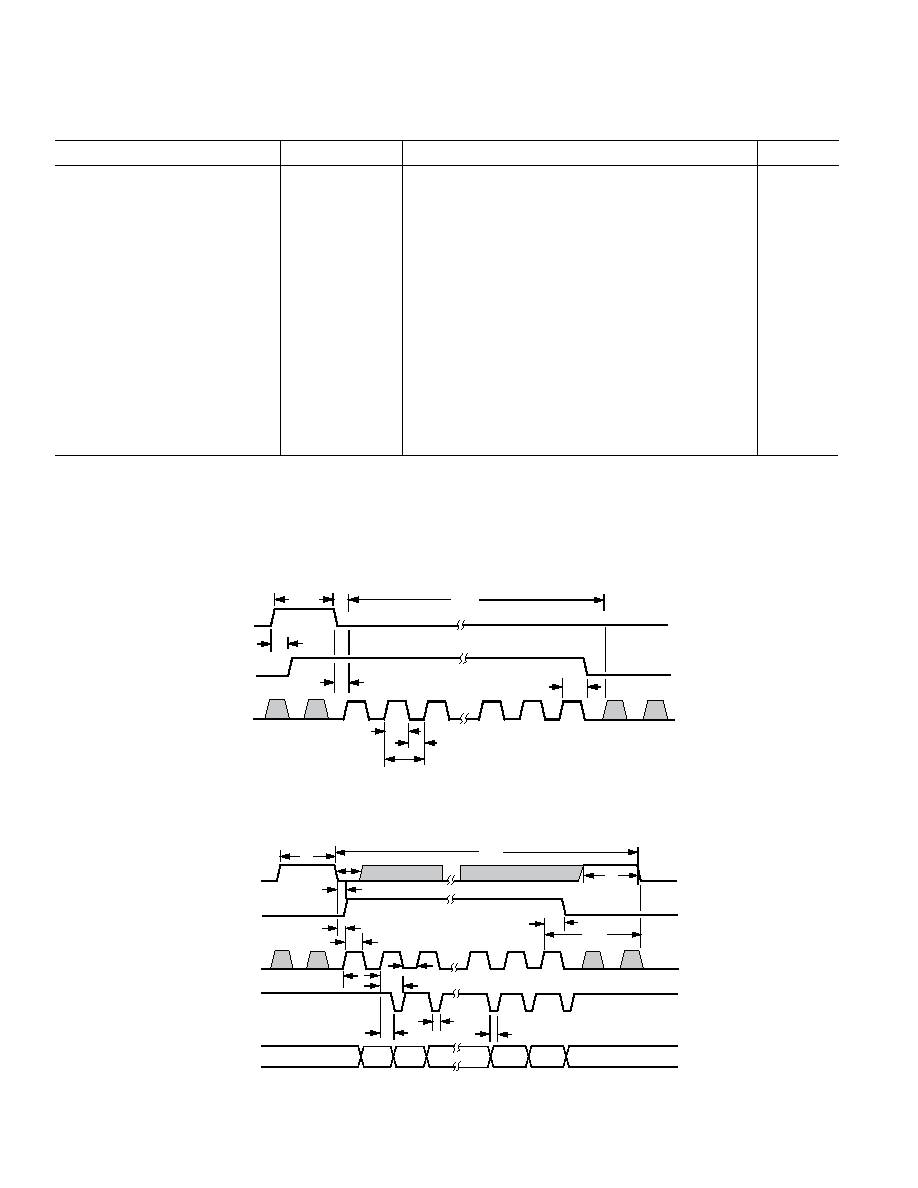

CAL

(INPUT)

BUSY

(OUTPUT)

CLK

*

(INPUT)

t

CT

t

CALH

t

CALB

t

CB

t

FCD

85530

85531

85532

1

23

t

CL

t

CH

t

CLK

*SHADED PORTIONS OF INPUT SIGNALS ARE OPTIONAL. FOR BEST PERFORMANCE, WE

RECOMMEND THAT THESE SIGNALS BE HELD LOW EXCEPT WHEN EXPLICITY SHOWN HIGH.

Figure 1. Calibration Timing

t

CB

BUSY

(OUTPUT)

t

FCD

t

CH

*SHADED PORTIONS OF INPUT SIGNALS ARE OPTIONAL. FOR BEST PERFORMANCE, WE

RECOMMEND THAT THESE SIGNALS BE HELD LOW EXCEPT WHEN EXPLICITY SHOWN HIGH.

SAMPLE*

(INPUT)

t

S

CLK

*

(INPUT)

1

23

15

16

17

t

S

t

LCS

MSB

BIT

2

BIT

15

BIT

13

BIT

14

BIT

16

SCLK

(OUTPUT)

SDATA

(OUTPUT)

OLD BIT 16

t

C

t

CD

t

SCL

t

DSH

t

SB

t

SL

t

CLK

t

CSH

t

CL

Figure 2. General Conversion Timing

相关PDF资料 |

PDF描述 |

|---|---|

| VE-JWY-EX | CONVERTER MOD DC/DC 3.3V 49.5W |

| 0210391057 | CABLE JUMPER 1MM .076M 35POS |

| ECM30DCMH | CONN EDGECARD 60POS .156 WW |

| VE-JWY-EW | CONVERTER MOD DC/DC 3.3V 66W |

| ECM30DCMD | CONN EDGECARD 60POS .156 WW |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD677JD | 功能描述:IC ADC 16BIT SAMPLING 16-CDIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD677JN | 功能描述:IC ADC 16BIT SAMPLING 16-DIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD677JNZ | 功能描述:IC ADC 16BIT SAMPLING 16-DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD677JNZ | 制造商:Analog Devices 功能描述:IC 16-BIT ADC |

| AD677JR | 功能描述:IC ADC 16BIT 100KSPS 28-SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

发布紧急采购,3分钟左右您将得到回复。