参数资料

| 型号: | AD7243ARZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/12页 |

| 文件大小: | 0K |

| 描述: | IC DAC 12BIT W/AMP W/REF 16-SOIC |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 47 |

| 系列: | DACPORT® |

| 设置时间: | 10µs |

| 位数: | 12 |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 电压电源: | 双 ± |

| 功率耗散(最大): | 100mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 16-SOIC W |

| 包装: | 管件 |

| 输出数目和类型: | 1 电压,单极;1 电压,双极 |

| 采样率(每秒): | 300k |

| 产品目录页面: | 784 (CN2011-ZH PDF) |

REV. A

–7–

AD7243

Although 16 bits of data are clocked into the input register, only

the latter 12 bits get transferred into the DAC latch. The first 4

bits in the 16 bit stream are don’t cares since their value does

not affect the DAC latch data. Therefore, the data format is 4

don’t cares followed by the 12-bit data word with the LSB as

the last bit in the serial stream.

There are two ways in which the DAC latch and hence the ana-

log output may be updated. The status of the

LDAC input is

examined after

SYNC is taken low. Depending on its status, one

of two update modes is selected.

If

LDAC = 0, then the automatic update mode is selected. In

this mode the DAC latch and analog output are updated auto-

matically when the last bit in the serial data stream is clocked in.

The update thus takes place on the sixteenth falling SCLK edge.

If

LDAC = 1, then the automatic update is disabled and the

DAC latch is updated by taking

LDAC low any time after the

16-bit data transfer is complete. The update now occurs on the

falling edge of

LDAC. Note that the LDAC input must be taken

back high again before the next data transfer is initiated.

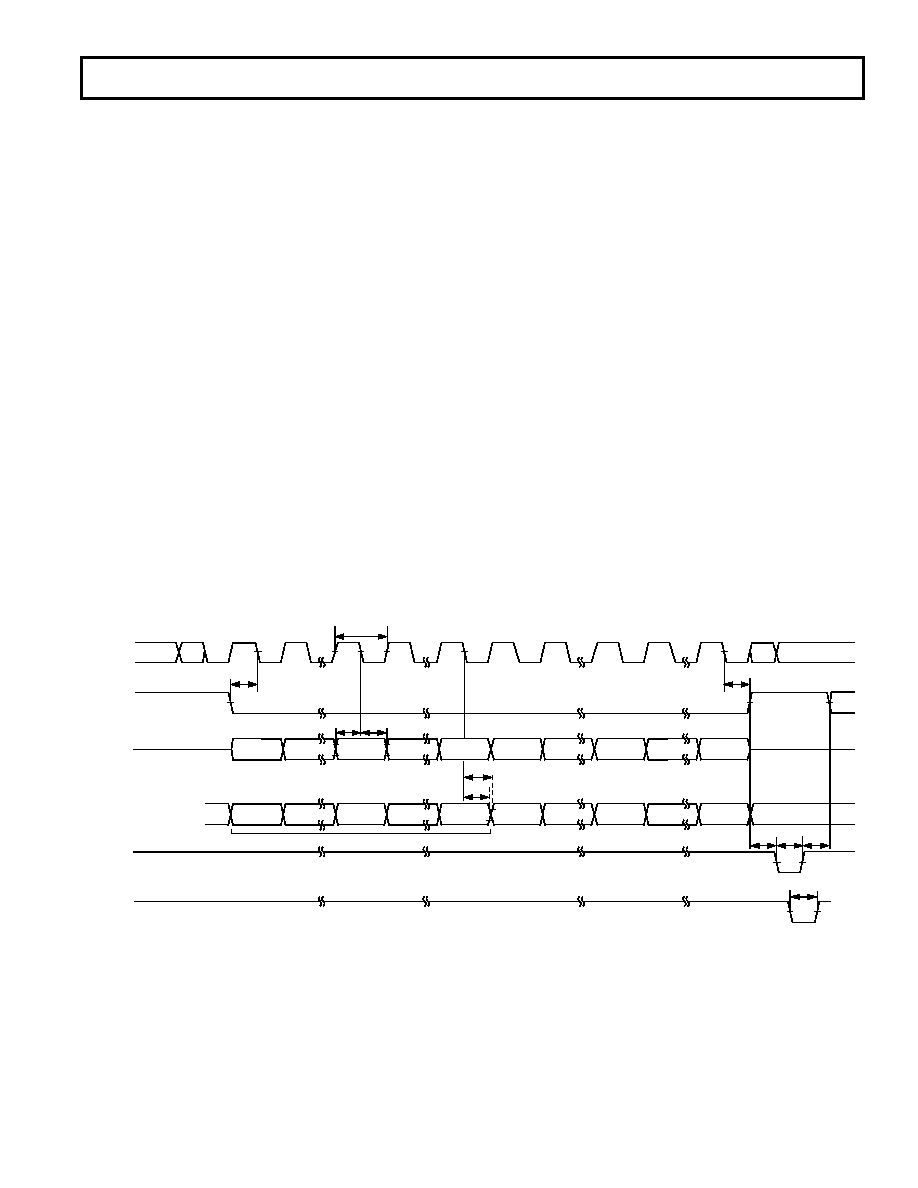

Serial Data Loading Format (Daisy-Chain Mode)

By connecting DCEN high the daisy-chain mode is enabled.

This mode of operation is designed for multi-DAC systems

where several AD7243s may be connected in cascade (see Fig-

ure 16). In this mode the internal gating circuitry on SCLK is

disabled, and a serial data output facility is enabled. The inter-

nal gating signal is permanently active (low) so that the SCLK

signal is continuously applied to the input shift register when

SYNC is low. The data is clocked into the register on each fall-

ing SCLK edge after

SYNC going low. If more than 16 clock

pulses are applied, the data ripples out of the shift register and

appears on the SDO line. By connecting this line to the SDIN

input on the next AD7243 in the chain, a multi-DAC interface

may be constructed. Sixteen SCLK pulses are required for each

DAC in the system. Therefore, the total number of clock cycles

must equal 16N where N is the total number of devices in the

chain. When the serial transfer to all devices is complete,

SYNC

should be taken high. This prevents any further data being

clocked into the input register.

A continuous SCLK source may be used if it can be arranged

that

SYNC is held low for the correct number of clock cycles.

Alternatively, a burst clock containing the exact number of clock

cycles may be used and

SYNC taken high some time later.

When the transfer to all input registers is complete, a common

LDAC signal updates all DAC latches with the lower 12 bits of

data in each input register. All analog outputs are therefore up-

dated simultaneously on the falling edge of

LDAC.

Clear Function (

CLR)

The clear function bypasses the input shift register and loads the

DAC Latch with all 0s. It is activated by taking

CLR low. In all

ranges except the Offset Binary bipolar range (–5 V to +5 V) the

output voltage is reset to 0 V. In the offset binary bipolar range

the output is set to –REFIN. The clear function is especially

useful at power-up as it enables the output to be reset to a

known state.

SCLK

DB11 (N)

MSB

DB0 (N)

LSB

* = DON'T CARE

SDIN

SYNC

LDAC

CLR

DB0 (N)

LSB

SDO

DB15 (N)*

DB15*

(N + 1)

DB11 (N + 1)

MSB

DB0 (N + 1)

LSB

UNDEFINED

DB15 (N)*

DB11 (N)

MSB

t1

t2

t3

t5

t4

t11

t6

t7

t8

t9

t10

Figure 8. Timing Diagram (Daisy-Chain Mode)

相关PDF资料 |

PDF描述 |

|---|---|

| MS27508E24B4PA | CONN RCPT 56POS BOX MNT W/PINS |

| ICS843003AGI-01LFT | IC SYNTHESIZER LVPECL 24-TSSOP |

| AD7541AKNZ | IC DAC 12BIT MULT MONO 18-DIP |

| SI5338H-A-GM | IC CLK GEN I2C BUS PROG 24QFN |

| MS3454W14S-9S | CONN RCPT 2POS JAM NUT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7243ARZ | 制造商:Analog Devices 功能描述:IC, DAC, 12BIT, 300KSPS, SOIC-16 |

| AD7243ARZ-REEL | 功能描述:IC SRL DAC 12BIT LC2MOS 16-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:DACPORT® 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

| AD7243BN | 功能描述:IC DAC 12BIT W/AMP W/REF 16-DIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:DACPORT® 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD7243BNZ | 功能描述:IC DAC 12BIT AMP/REF 16DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:DACPORT® 标准包装:1 系列:- 设置时间:4.5µs 位数:12 数据接口:串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOICN 包装:剪切带 (CT) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):* 其它名称:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND |

| AD7243BQ | 功能描述:IC DAC 12BIT W/AMP W/REF 16-CDIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:DACPORT® 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

发布紧急采购,3分钟左右您将得到回复。