- 您现在的位置:买卖IC网 > PDF目录373897 > AD73322AST (ANALOG DEVICES INC) Low Cost, Low Power CMOS General-Purpose Dual Analog Front End PDF资料下载

参数资料

| 型号: | AD73322AST |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 通信及网络 |

| 英文描述: | Low Cost, Low Power CMOS General-Purpose Dual Analog Front End |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP44 |

| 封装: | PLASTIC, LQFP-44 |

| 文件页数: | 12/40页 |

| 文件大小: | 437K |

| 代理商: | AD73322AST |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

REV. 0

AD73322L

–12–

F

B

= 4kHz

F

SINIT

= DMCLK/8

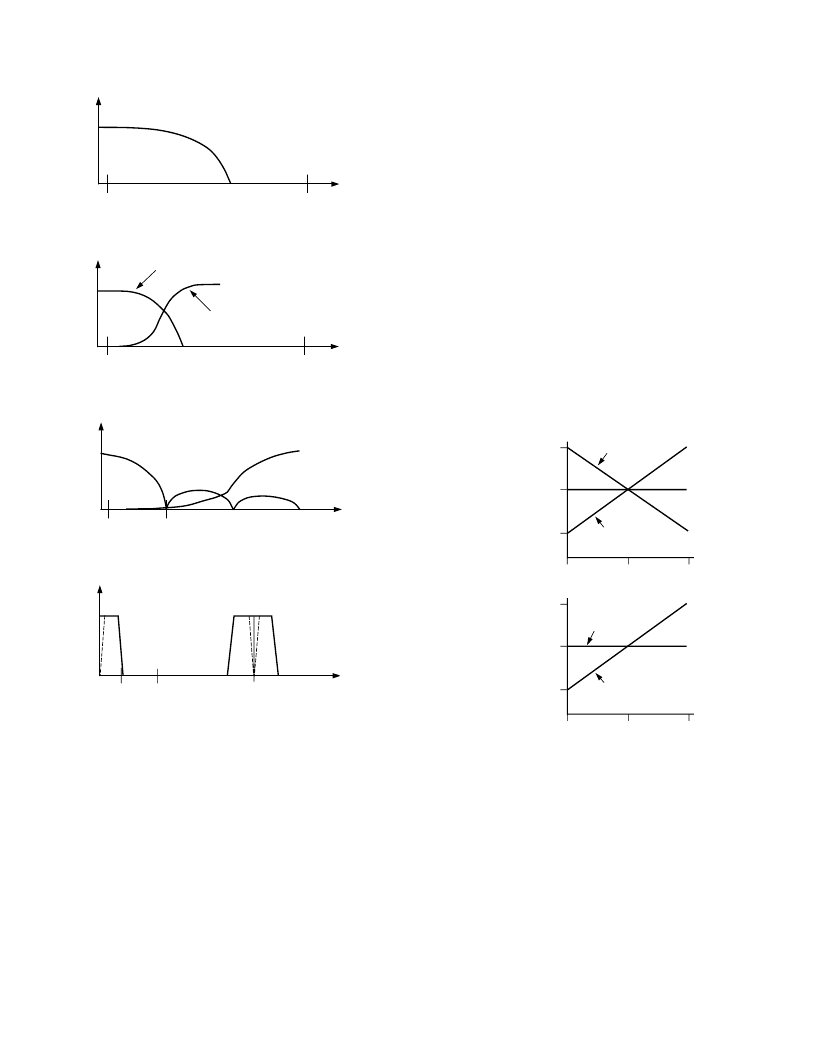

a. Analog Antialias Filter Transfer Function

F

B

= 4kHz

F

SINIT

= DMCLK/8

NOISE TRANSFER FUNCTION

SIGNAL TRANSFER FUNCTION

b. Analog Sigma-Delta Modulator Transfer Function

F

B

= 4kHz

F

SINTER

= DMCLK/256

c. Digital Decimator Transfer Function

F

B

= 4kHz

F

SINTER

= DMCLK/256

F

SFINAL

= 8kHz

d. Final Filter LPF (HPF) Transfer Function

Figure 7. ADC Frequency Responses

Decimation Filter

The digital filter used in the AD73322L carries out two important

functions. Firstly, it removes the out-of-band quantization

noise, which is shaped by the analog modulator and secondly,

it decimates the high frequency bit stream to a lower rate 16-

bit word.

The antialiasing decimation filter is a sinc-cubed digital filter

that reduces the sampling rate from DMCLK/8 to DMCLK/256,

and increases the resolution from a single bit to 15 bits or greater

(depending on chosen sampling rate). Its Z transform is given as:

[(1

–

Z

–

N

)/(1

–

Z

–

1

)]

3

where

N

is set by the sampling rate (

N

= 32 @ 64 kHz sam-

pling. . .

N

= 256 @ 8 kHz sampling). Thus when the sampling

rate is 64 kHz, a minimal group delay of 25

μ

s can be achieved.

Word growth in the decimator is determined by the sampling

rate. At 64 kHz sampling, where the oversampling ratio between

sigma-delta modulator and decimator output equals 32, there

are five bits per stage of the three-stage Sinc3 filter. Due to symme-

try within the sigma-delta modulator, the LSB will always be a

zero; therefore, the 16-bit ADC output word will have 2 LSBs

equal to zero, one due to the sigma-delta symmetry and the

other being a padding zero to make up the 16-bit word. At

lower sampling rates, decimator word growth will be greater

than the 16-bit sample word, therefore truncation occurs in

transferring the decimator output as the ADC word. For example,

at 8 kHz sampling, word growth reaches 24 bits due to the OSR

of 256 between sigma-delta modulator and decimator output.

This yields eight bits per stage of the three-stage Sinc3 filter.

ADC Coding

The ADC coding scheme is in twos complement format (see

Figure 8). The output words are formed by the decimation

filter, which grows the word length from the single-bit output

of the sigma-delta modulator to a word length of up to 24 bits

(depending on decimation rate chosen), which is the final out-

put of the ADC block. In Data Mode this value is truncated to

16 bits for output on the Serial Data Output (SDO) pin.

V

REF

+ (V

REF

0.32875)

V

REF

V

REF

–

(V

REF

0.32875)

10...00

00...00

01...11

ADC CODE DIFFERENTIAL

ANALOG

INPUT

V

INN

V

INP

V

REF

+ (V

REF

0.6575)

V

REF

–

(V

REF

0.6575)

10...00

00...00

01...11

ADC CODE SINGLE-ENDED

ANALOG

INPUT

V

INP

V

INN

Figure 8. ADC Transfer Function

In mixed Control/Data Mode, the resolution is fixed at 15 bits,

with the MSB of the 16-bit transfer being used as a flag bit to

indicate either control or data in the frame.

Decoder Channel

The decoder channels consist of digital interpolators, digital

sigma-delta modulators, single-bit digital-to-analog converters

(DAC), analog smoothing filters and programmable gain ampli-

fiers with differential outputs.

DAC Coding

The DAC coding scheme is in twos complement format with

0x7FFF being full-scale positive and 0x8000 being full-

scale negative.

相关PDF资料 |

PDF描述 |

|---|---|

| AD73322LAR | Low Cost, Low Power CMOS General-Purpose Dual Analog Front End |

| AD73322LAST | Low Cost, Low Power CMOS General-Purpose Dual Analog Front End |

| AD73322EB | Low Power 10MHz Current Feedback Amplifier; Package: SO; No of Pins: 8; Temperature Range: 0°C to +70°C |

| AD73322EZ | Precision Rail-to-Rail Input and Output Op Amp; Package: SO; No of Pins: 8; Temperature Range: 0°C to +70°C |

| AD73322LYR | Low Cost, Low Power CMOS General-Purpose Dual Analog Front End |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD73322AST-REEL | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 2DAC 16-Bit 44-Pin LQFP T/R |

| AD73322ASTZ | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 2DAC 16-Bit 44-Pin LQFP |

| AD73322EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost Low Power CMOS General-Purpose Dual Analog Front End(386.88 k) |

| AD73322EZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost Low Power CMOS General-Purpose Dual Analog Front End(386.88 k) |

| AD73322L | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost, Low Power CMOS General-Purpose Dual Analog Front End |

发布紧急采购,3分钟左右您将得到回复。