- 您现在的位置:买卖IC网 > PDF目录10212 > AD7357BRUZ-RL (Analog Devices Inc)IC ADC 14BITDUAL 4.MSPS 16TSSOP PDF资料下载

参数资料

| 型号: | AD7357BRUZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/21页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BITDUAL 4.MSPS 16TSSOP |

| 设计资源: | DC-Coupled, Single-Ended-to-Differential Conversion Using AD8138 and AD7357 (CN0061) |

| 标准包装: | 2,500 |

| 位数: | 14 |

| 采样率(每秒): | 4.2M |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 59mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 个差分,双极 |

AD7357

Rev. B | Page 15 of 20

MODES OF OPERATION

The AD7357 mode of operation is selected by controlling the

logic state of the CS signal during a conversion. There are three

possible modes of operation: normal mode, partial power-down

mode, and full power-down mode. After a conversion has been

initiated, the point at which CS is pulled high determines which

power-down mode, if any, the device enters. Similarly, if already

in a power-down mode, CS can control whether the device

returns to normal operation or remains in a power-down mode.

These modes of operation are designed to provide flexible power

management options. These options can be chosen to optimize

the power dissipation/throughput rate ratio for the differing

application requirements.

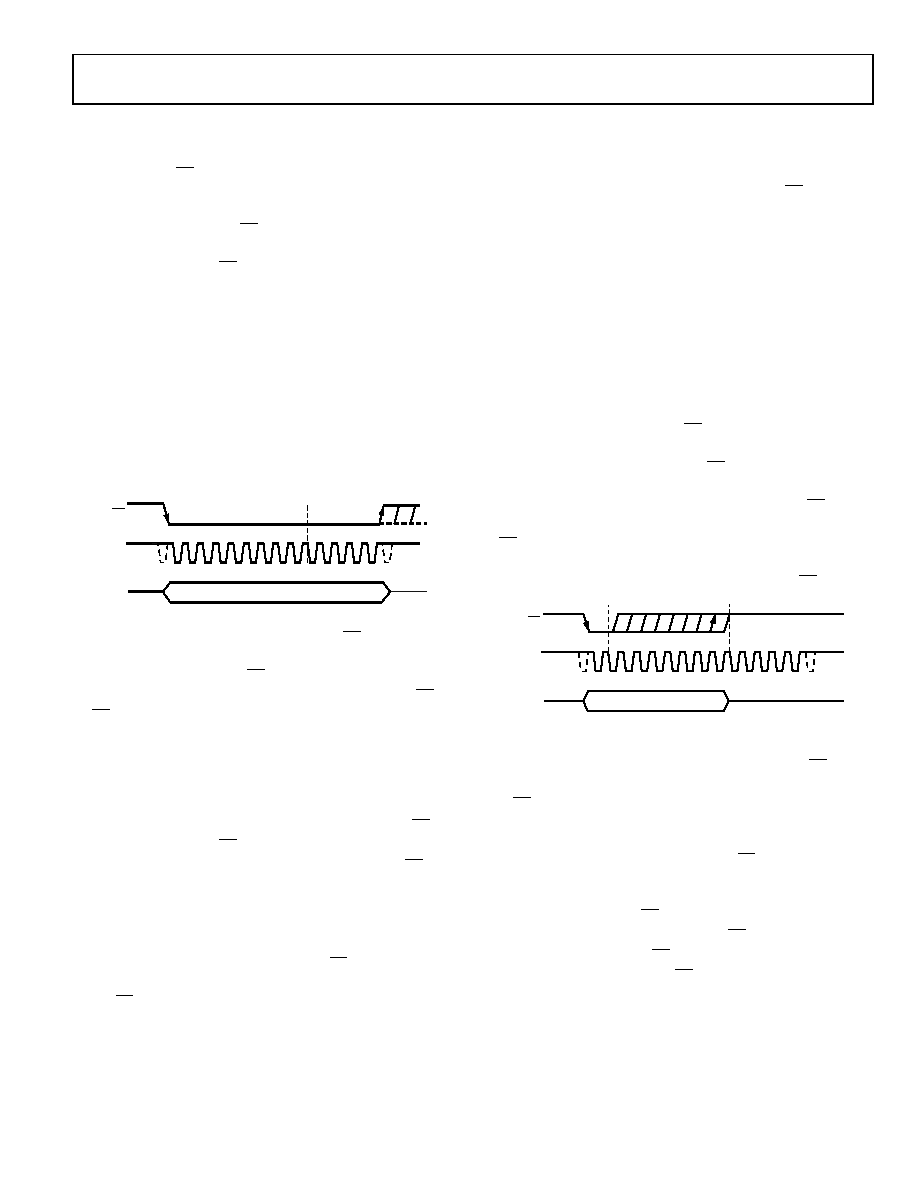

NORMAL MODE

Normal mode is intended for applications needing the fastest

throughput rates. The user does not have to worry about any

power-up times because the AD7357 remains fully powered at

all times. Figure 24 shows the general diagram of the operation

of the AD7357 in this mode.

SCLK

LEADING ZEROS + CONVERSION RESULT

CS

1

10

14

07

75

7-

01

8

SDATAA

SDATAB

Figure 24. Normal Mode Operation

The conversion is initiated on the falling edge of CS, as described

in the

section. To ensure that the part remains

fully powered up at all times,

CS must remain low until at least

10 SCLK falling edges have elapsed after the falling edge of CS.

If CS is brought high any time after the 10th SCLK falling edge

but before the 16th SCLK falling edge, the part remains powered

up, but the conversion is terminated and SDATA and SDATAB

go back into three-state. 16 serial clock cycles are required to

complete the conversion and access the conversion result for

the AD7357. The SDATA lines do not return to three-state

after 16 SCLK cycles have elapsed, but instead do so when

A

CS

is brought high again. If CS is left low for another 2 SCLK

cycles, two trailing zeros are clocked out after the data. If CS

is left low for a further 16 SCLK cycles, the result for the other

ADC on board is also accessed on the same SDATA line as

shown in

(see the

section).

When 32 SCLK cycles have elapsed, the SDATA line returns to

three-state on the 32nd SCLK falling edge. If CS is brought high

prior to this, the SDATA line returns to three-state at that point.

Thus, CS may idle low after 32 SCLK cycles until it is brought

high again sometime prior to the next conversion, if so desired,

because the bus still returns to three-state upon completion of

the dual result read.

When a data transfer is complete and SDATAA and SDATAB

have returned to three-state, another conversion can be initiated

after the quiet time, tQUIET, has elapsed by bringing CS low again

(assuming the required acquisition time has been allowed).

PARTIAL POWER-DOWN MODE

This mode is intended for use in applications where slower

throughput rates are required. Either the ADC is powered

down between each conversion, or a series of conversions

can be performed at a high throughput rate and the ADC is

then powered down for a relatively long duration between

these bursts of several conversions. When the AD7357 is in

partial power-down, all analog circuitry is powered down

except for the on-chip reference and reference buffers.

To enter partial power-down mode, the conversion process

must be interrupted by bringing CS high anywhere after the

second falling edge of SCLK and before the 10th falling edge of

SCLK, as shown in

. When

CS is brought high in this

window of SCLKs, the part enters partial power-down mode,

the conversion that was initiated by the falling edge of CS is

terminated, and SDATA and SDATAB go back into three-state. If

A

CS is brought high before the second SCLK falling edge, the

part remains in normal mode and does not power down. This

avoids accidental power-down due to glitches on the CS line.

SCLK

THREE-STATE

CS

SDATAA

SDATAB

11

10

4

2

0

775

7-

0

19

Figure 25. Entering Partial Power-Down Mode

To exit this mode of operation and to power up the AD7357

again, perform a dummy conversion. On the falling of CS, the

device begins to power up and continues to power up as long

as CS is held low until after the falling edge of the 10th SCLK.

The device is fully powered up after approximately 200 ns

elapses (or one full conversion), and valid data results from the

next conversion, as shown in

. If

CS is brought high

before the second falling edge of SCLK, the AD7357 again goes

into partial power-down mode. This avoids accidental power-

up due to glitches on the CS line. Although the device may

begin to power up on the falling edge of CS, it powers down

again on the rising edge of CS. If the AD7357 is already in

partial power-down mode and CS is brought high between

the second and 10th falling edges of SCLK, the device enters

full power-down mode.

相关PDF资料 |

PDF描述 |

|---|---|

| SP3083EEN-L/TR | IC TXRX RS485/RS422 ESD 14NSOIC |

| SP3081EEN-L/TR | IC TXRX RS485/RS422 ESD 8NSOIC |

| SP3080EEN-L/TR | IC TXRX RS485/RS422 ESD 14NSOIC |

| AD7661ACPZ | IC ADC 16BIT W/REF 48LFCSP |

| SP3077EEN-L/TR | IC TXRX RS485/RS422 ESD 8NSOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7357WYRUZ | 制造商:Analog Devices 功能描述:ADC Dual SAR 4.2Msps 14-bit Serial 16-Pin TSSOP 制造商:Analog Devices 功能描述:14-BIT DUAL DIFF SIMULT 5 MSPS ADC I.C. - Rail/Tube 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述:IC ADC 14BIT SRL 5MSPS 16TSSOP 制造商:Analog Devices 功能描述:Analog to Digital Converters - ADC 14-Bit Dual Diff Simult 5 MSPS 制造商:Analog Devices 功能描述:14-Bit Dual Diff Simult 5 MSPS ADC I.C. |

| AD7357WYRUZ-RL | 功能描述:模数转换器 - ADC 14-Bit Dual Diff Simult 5 MSPS RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

| AD7357YRUZ | 功能描述:IC ADC DUAL14BIT 4.2MSPS 16TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD7357YRUZ-500RL7 | 功能描述:IC ADC DUAL14BIT 4.2MSPS 16TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7357YRUZ-RL | 功能描述:IC ADC DUAL14BIT 4.2MSPS 16TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

发布紧急采购,3分钟左右您将得到回复。