- 您现在的位置:买卖IC网 > PDF目录10681 > AD7401AYRWZ (Analog Devices Inc)IC MODULATOR SIGMA-DELTA 16SOIC PDF资料下载

参数资料

| 型号: | AD7401AYRWZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/20页 |

| 文件大小: | 0K |

| 描述: | IC MODULATOR SIGMA-DELTA 16SOIC |

| 标准包装: | 47 |

| 位数: | 16 |

| 采样率(每秒): | 20M |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 93.5mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 16-SOIC W |

| 包装: | 管件 |

| 输入数目和类型: | 1 个差分,双极 |

| 产品目录页面: | 798 (CN2011-ZH PDF) |

AD7401A

Rev. C | Page 16 of 20

DIGITAL FILTER

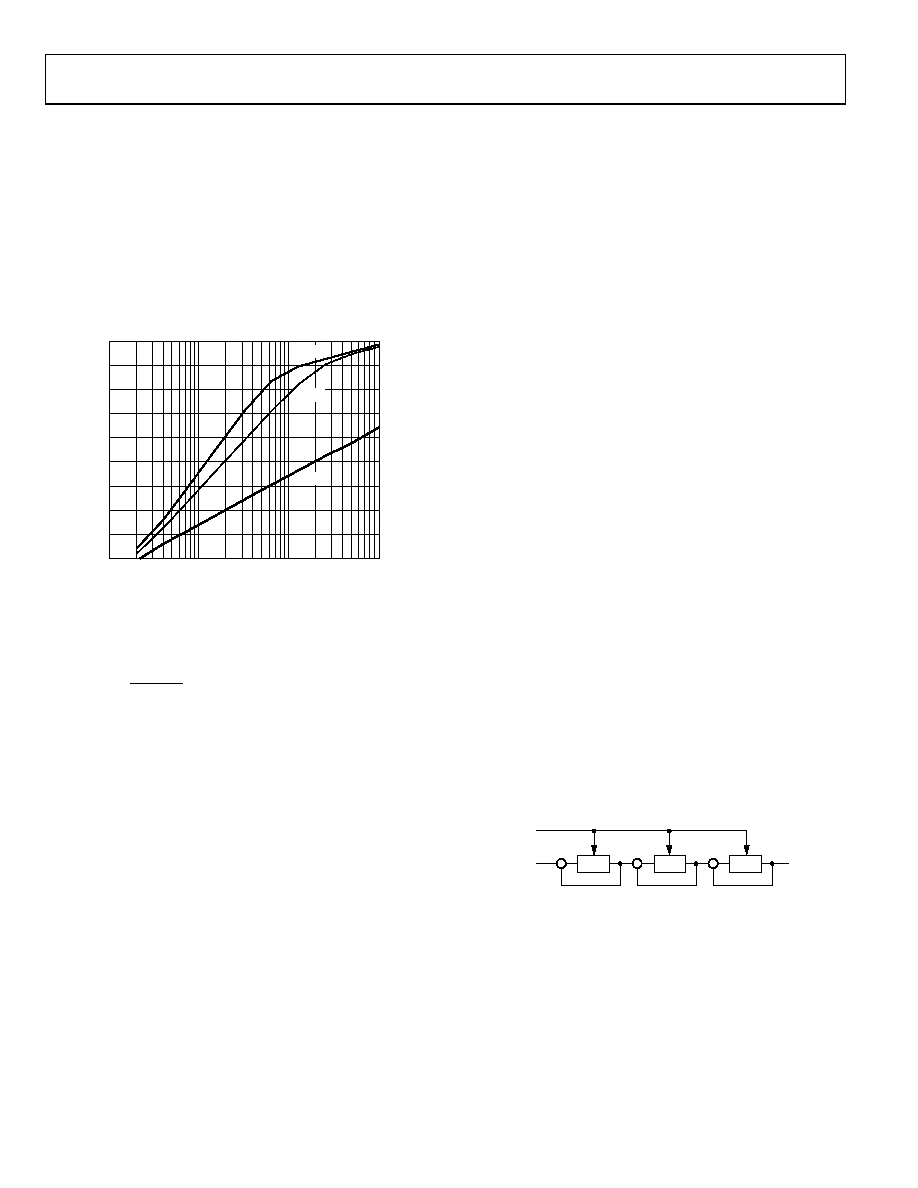

The overall system resolution and throughput rate is determined

by the filter selected and the decimation rate used. The higher

the decimation rate, the greater the system accuracy, as illus-

trated in Figure 26. However, there is a tradeoff between accuracy

and throughput rate and, therefore, higher decimation rates

result in lower throughput solutions. Note that for a given

bandwidth requirement, a higher MCLKIN frequency can allow

for higher decimation rates to be used, resulting in higher SNR

performance.

80

70

60

50

40

30

20

10

0

90

10

100

1k

1

DECIMATION RATE

S

NR

(

d

B)

SINC3

SINC2

SINC1

07

33

2-

02

6

Figure 26. SNR vs. Decimation Rate for Different Filter Types

A sinc3 filter is recommended for use with the AD7401A. This

filter can be implemented on an FPGA or a DSP.

(

)

()

3

1

)

(

=

Z

z

H

DR

where DR is the decimation rate.

The following Verilog code provides an example of a sinc3 filter

implementation on a Xilinx Spartan-II 2.5 V FPGA. This code

can possibly be compiled for another FPGA, such as an Altera

device. Note that the data is read on the negative clock edge in

this case, although it can be read on the positive edge, if

preferred.

/*`Data is read on negative clk edge*/

module DEC256SINC24B(mdata1, mclk1, reset,

DATA);

input

mclk1;

/*used to clk filter*/

input

reset;

/*used to reset filter*/

input

mdata1;

/*ip data to be

filtered*/

output [15:0] DATA;

/*filtered op*/

integer location;

integer info_file;

reg [23:0]

ip_data1;

reg [23:0]

acc1;

reg [23:0]

acc2;

reg [23:0]

acc3;

reg [23:0]

acc3_d1;

reg [23:0]

acc3_d2;

reg [23:0]

diff1;

reg [23:0]

diff2;

reg [23:0]

diff3;

reg [23:0]

diff1_d;

reg [23:0]

diff2_d;

reg [15:0]

DATA;

reg [7:0]

word_count;

reg word_clk;

reg init;

/*Perform the Sinc ACTION*/

always @ (mdata1)

if(mdata1==0)

ip_data1 <= 0;

/* change from a 0

to a -1 for 2's comp */

else

ip_data1 <= 1;

/*ACCUMULATOR (INTEGRATOR)

Perform the accumulation (IIR) at the speed

of the modulator.

MCLKIN

IP_DATA1

ACC1+

ACC2+

ACC3+

+

Z

+

Z

+

Z

07

33

2-

02

7

Figure 27. Accumulator

相关PDF资料 |

PDF描述 |

|---|---|

| AD790JRZ-REEL | IC COMPARATOR PREC HS 8-SOIC |

| AD9203ARUZ | IC ADC 10BIT 40MSPS 3V 28-TSSOP |

| LT1720IDD#TRPBF | IC COMPARATOR DUAL HS 3/5V 8-DFN |

| LT1720IDD#TR | IC COMPARATOR DUAL HS 3/5V 8-DFN |

| AD7277BUJZ-500RL7 | IC ADC 10BIT 3MSPS TSOT23-6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7401AYRWZ-RL | 功能描述:IC MODULATOR SIGMA-DELTA 16SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7401BRW | 制造商:Analog Devices 功能描述: |

| AD7401YRW | 制造商:Analog Devices 功能描述: |

| AD7401YRW-REEL | 功能描述:INTEGRATED CIRCUIT 制造商:analog devices inc. 系列:* 包装:带卷(TR) 零件状态:最後搶購 安装类型:表面贴装 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商器件封装:16-SOIC 标准包装:1 |

| AD7401YRWZ | 功能描述:IC MODULATOR SIGMA-DELTA 16SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

发布紧急采购,3分钟左右您将得到回复。