参数资料

| 型号: | AD7608BSTZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 19/32页 |

| 文件大小: | 0K |

| 描述: | IC DAS W/ADC 18BIT 8CH 64LQFP |

| 标准包装: | 1,500 |

| 类型: | 数据采集系统(DAS),ADC |

| 分辨率(位): | 18 b |

| 采样率(每秒): | 200k |

| 数据接口: | DSP,MICROWIRE?,并联,QSPI?,串行,SPI? |

| 电压电源: | 模拟和数字 |

| 电源电压: | 2.3 V ~ 5.25 V,4.75 V ~ 5.25 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

AD7608

Data Sheet

Rev. A | Page 26 of 32

DIGITAL FILTER

The AD7608 contains an optional digital first-order sinc filter

that should be used in applications where slower throughput

rates are used or where higher signal-to-noise ratio or dynamic

range is desirable. The oversampling ratio of the digital filter is

controlled using the oversampling pins, OS [2:0] (see Table 8).

OS 2 is the MSB control bit, and OS 0 is the LSB control bit.

Table 8 provides the oversampling bit decoding to select the

different oversample rates. The OS pins are latched on the falling

edge of BUSY. This sets the oversampling rate for the next

conversion (see Figure 45). In addition to the oversampling

function, the output result is decimated to 18-bit resolution.

If the OS pins are set to select an OS ratio of 8, the next

CONVST x rising edge takes the first sample for each channel,

and the remaining seven samples for all channels are taken with

an internally generated sampling signal. These samples are then

averaged to yield an improvement in SNR performance. Table 8

shows typical SNR performance for both the ±10 V and the

±5 V range. As Table 8 indicates, there is an improvement in

SNR as the OS ratio increases. As the OS ratio increases, the

3 dB frequency is reduced, and the allowed sampling frequency

is also reduced. In an application where the required sampling

frequency is 10 kSPS, an OS ratio of up to 16 can be used. In

this case, the application sees an improvement in SNR, but the

input 3 dB bandwidth is limited to ~6 kHz.

The CONVST A and CONVST B pins must be tied/driven

together when oversampling is turned on. When the over-

sampling function is turned on, the BUSY high time for the

conversion process extends. The actual BUSY high time

depends on the oversampling rate selected: the higher

the oversampling rate, the longer the BUSY high, or total

conversion time (see Table 3).

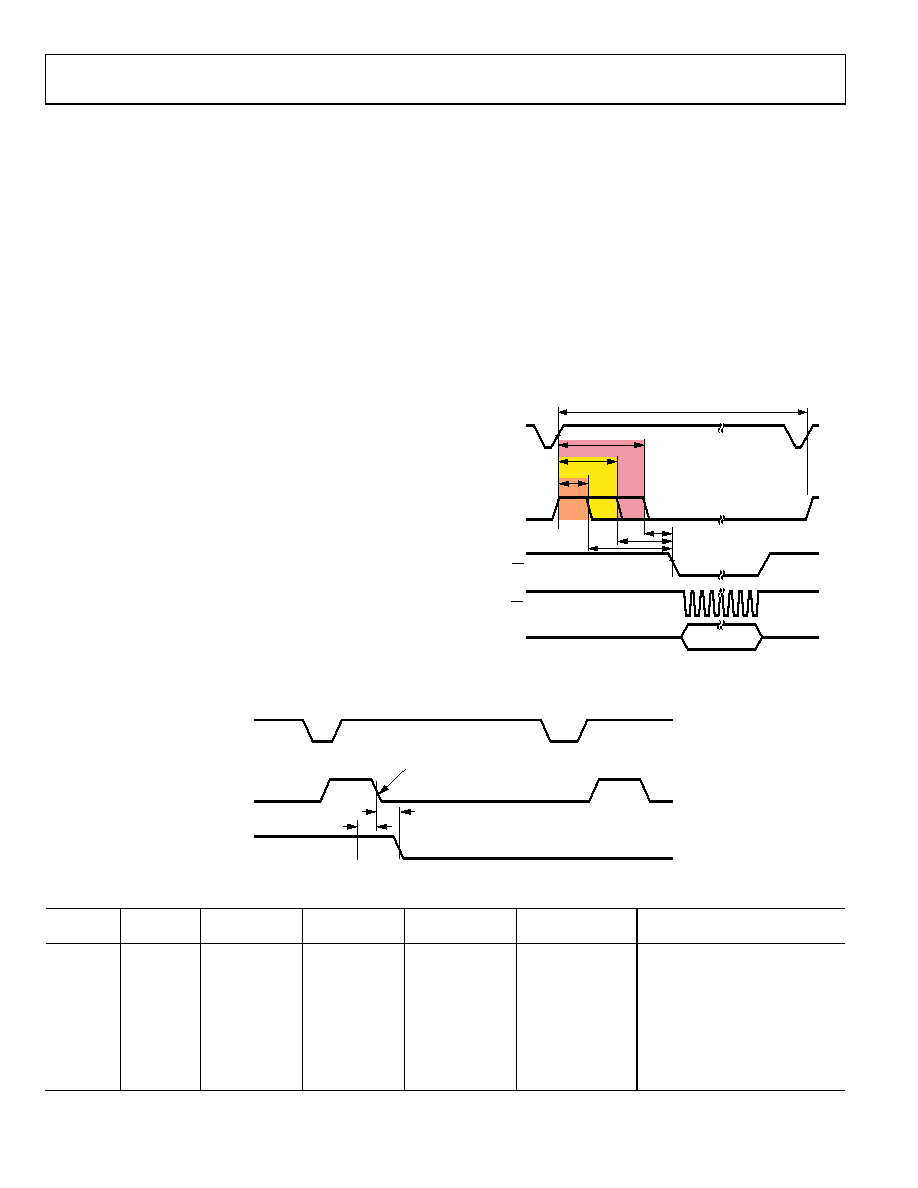

Figure 44 shows that the conversion time extends as the over-

sampling rate is increased, and the BUSY signal lengthens for the

different oversampling rates. For example, a sampling frequency

of 10 kSPS yields a cycle time of 100 s. Figure 44 shows OS × 2

and OS × 4; for a 10 kSPS example, there is adequate cycle time to

further increase the oversampling rate and yield greater improve-

ments in SNR performance. In an application where the initial

sampling or throughput rate is at 200 kSPS, for example, and

oversampling is turned on, the throughput rate must be reduced

to accommodate the longer conversion time and to allow for the

read. To achieve the fastest throughput rate possible when over-

sampling is turned on, the read can be performed during the

BUSY high time. The falling edge of BUSY is used to update the

output data registers with the new conversion data; therefore, the

reading of conversion data should not occur on this edge.

CS

RD

DATA:

DB[15:0]

BUSY

CONVST A,

CONVST B

tCYCLE

tCONV

4s

t4

9s

19s

OS = 0 OS = 2 OS = 4

08938-

043

Figure 44. No Oversampling, Oversampling × 2, and Oversampling × 4 While

Using Read After Conversion

CONVST A,

CONVST B

BUSY

OS x

tOS_SETUP

tOS_HOLD

CONVERSION N

CONVERSION N + 1

OVERSAMPLE RATE

LATCHED FOR CONVERSION N + 1

08938-

042

Figure 45. OS Pin Timing

Table 8. Oversample Bit Decoding

OS [2:0]

OS Ratio

SNR ±5 V

Range (dB)1

SNR ±10 V

Range (dB)1

3 dB BW ±5 V

Range (kHz)

3 dB BW ±10 V

Range (kHz)

Maximum Throughput

CONVST x Frequency (kHz)

000

No OS

90.5

91.2

15

22

200

001

2

92.5

93.4

15

22

100

010

4

94.45

95.7

13.7

18.5

50

011

8

96.5

98

10.3

11.9

25

100

16

99.1

100.4

6

12.5

101

32

101.7

102.8

3

6.25

110

64

103

103.5

1.5

3.125

111

Invalid

1

SNR values taken with a full scale 100 Hz input signal.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7609BSTZ-RL | IC DAS W/ADC 18BIT 8CH 64LQFP |

| AD760AQ | IC DAC 16BIT W/AMP SRL 28-CDIP |

| AD766AN | IC DAC 16BIT W/REF DSP 16-DIP |

| AD767BD | IC DAC 12BIT W/AMP 24-CDIP |

| AD768AR | IC DAC 16BIT 30MSPS 28-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7609 | 制造商:AD 制造商全称:Analog Devices 功能描述:8-Channel Differential DAS with 18-Bit |

| AD7609BSTZ | 功能描述:IC DAS 18BIT 8CHANNEL 64-LQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - ADCs/DAC - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 类型:数据采集系统(DAS) 分辨率(位):16 b 采样率(每秒):21.94k 数据接口:MICROWIRE?,QSPI?,串行,SPI? 电压电源:模拟和数字 电源电压:1.8 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(6x6) 包装:托盘 |

| AD7609BSTZ-RL | 功能描述:IC DAS W/ADC 18BIT 8CH 64LQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - ADCs/DAC - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 类型:数据采集系统(DAS) 分辨率(位):16 b 采样率(每秒):21.94k 数据接口:MICROWIRE?,QSPI?,串行,SPI? 电压电源:模拟和数字 电源电压:1.8 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(6x6) 包装:托盘 |

| AD760AN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital-to-Analog Converter |

| AD760AP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital-to-Analog Converter |

发布紧急采购,3分钟左右您将得到回复。