参数资料

| 型号: | AD7678ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/28页 |

| 文件大小: | 0K |

| 描述: | IC ADC 18BIT SAR W/BUFF 48LFCSP |

| 标准包装: | 1 |

| 系列: | PulSAR® |

| 位数: | 18 |

| 采样率(每秒): | 100k |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 26mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 托盘 |

| 输入数目和类型: | 1 个差分,双极 |

| 配用: | EVAL-AD7678CB-ND - BOARD EVALUATION FOR AD7678 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页

AD7678

Rev. A | Page 9 of 28

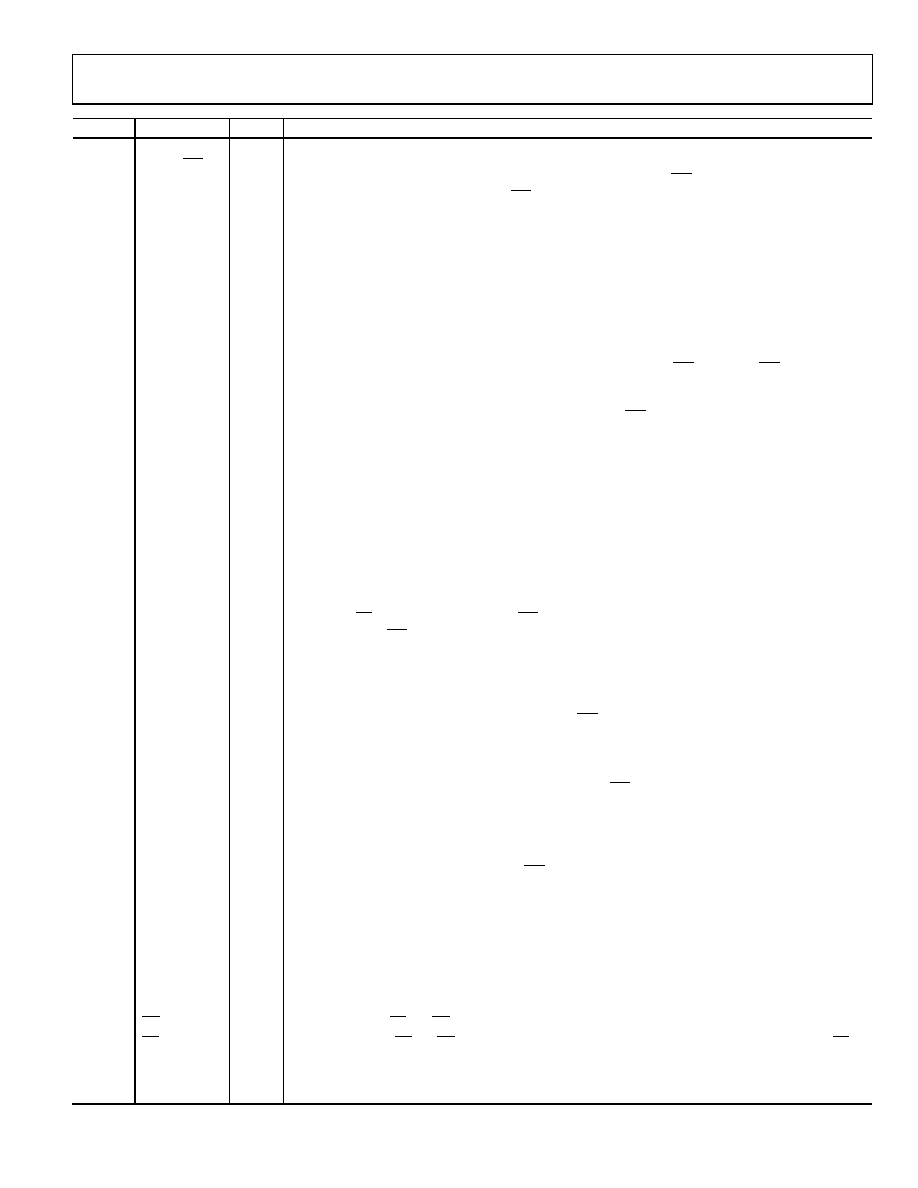

Pin No.

Mnemonic

Description

13

D6

or EXT/INT

DI/O

In all modes except MODE = 3, this output is used as Bit 6 of the parallel port data output bus.

When MODE = 3 (serial mode), this input, part of the serial port, is used as a digital select input for

choosing the internal data clock or an external data clock. With EXT/INT tied LOW, the internal clock is

selected on the SCLK output. With EXT/INT set to a logic HIGH, output data is synchronized to an

external clock signal connected to the SCLK input.

14

D7

or INVSYNC

DI/O

In all modes except MODE = 3, this output is used as Bit 7 of the parallel port data output bus.

When MODE = 3 (serial mode), this input, part of the serial port, is used to select the active state of the

SYNC signal. When LOW, SYNC is active HIGH. When HIGH, SYNC is active LOW.

15

D8

or INVSCLK

DI/O

In all modes except MODE = 3, this output is used as Bit 8 of the parallel port data output bus.

When MODE = 3 (serial mode), this input, part of the serial port, is used to invert the SCLK signal. It is

active in both master and slave modes.

16

D9

or RDC/SDIN

DI/O

In all modes except MODE = 3, this output is used as Bit 9 of the parallel port data output bus.

When MODE = 3 (serial mode), this input, part of the serial port, is used as either an external data

input or a read mode selection input depending on the state of EXT/INT. When EXT/INT is HIGH,

RDC/SDIN could be used as a data input to daisy-chain the conversion results from two or more ADCs

onto a single SDOUT line. The digital data level on SDIN is output on SDOUT with a delay of 18 SCLK

periods after the initiation of the read sequence. When EXT/INT is LOW, RDC/SDIN is used to select the

read mode. When RDC/SDIN is HIGH, the data is output on SDOUT during conversion. When

RDC/SDIN is LOW, the data can be output on SDOUT only when the conversion is complete.

17

OGND

P

Input/Output Interface Digital Power Ground.

18

OVDD

P

Output Interface Digital Power. Nominally at the same supply as the host interface (5 V or 3 V). Should

not exceed DVDD by more than 0.3 V.

19

DVDD

P

Digital Power. Nominally at 5 V.

20

DGND

P

Digital Power Ground.

21

D10

or SDOUT

DO

In all modes except MODE = 3, this output is used as Bit 10 of the parallel port data output bus.

When MODE = 3 (serial mode), this output, part of the serial port, is used as a serial data output

synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7678 provides the

conversion result, MSB first, from its internal shift register. The data format is determined by the logic

level of OB/2C. In serial mode when EXT/INT is LOW, SDOUT is valid on both edges of SCLK. In serial

mode when EXT/INT is HIGH and INVSCLK is LOW, SDOUT is updated on the SCLK rising edge and is

valid on the next falling edge; if INVSCLK is HIGH, SDOUT is updated on the SCLK falling edge and is

valid on the next rising edge.

22

D11

or SCLK

DI/O

In all modes except MODE = 3, this output is used as Bit 11 of the parallel port data output bus.

When MODE = 3 (serial mode), this pin, part of the serial port, is used as a serial data clock input or

output, depending upon the logic state of the EXT/INT pin. The active edge where the data SDOUT is

updated depends upon the logic state of the INVSCLK pin.

23

D12

or SYNC

DO

In all modes except MODE = 3, this output is used as Bit 12 of the parallel port data output bus.

When MODE = 3 (serial mode), this output, part of the serial port, is used as a digital output frame

synchronization for use with the internal data clock (EXT/INT = Logic LOW). When a read sequence is

initiated and INVSYNC is LOW, SYNC is driven HIGH and remains HIGH while the SDOUT output is

valid. When a read sequence is initiated and INVSYNC is HIGH, SYNC is driven LOW and remains LOW

while SDOUT output is valid.

24

D13

or RDERROR

DO

In all modes except MODE = 3, this output is used as Bit 13 of the parallel port data output bus.

In MODE = 3 (serial mode) and when EXT/INT is HIGH, this output, part of the serial port, is used as an

incomplete read error flag. In slave mode, when a data read is started and not complete when the

following conversion is complete, the current data is lost and RDERROR is pulsed high.

25–28

D[14:17]

DO

Bit 14 to Bit 17 of the Parallel Port Data Output Bus. These pins are always outputs regardless of the

interface mode.

29

BUSY

DO

Busy Output. Transitions HIGH when a conversion is started. Remains HIGH until the conversion is

complete and the data is latched into the on-chip shift register. The falling edge of BUSY could be

used as a data ready clock signal.

30

DGND

P

Must Be Tied to Digital Ground.

31

RD

DI

Read Data. When CS and RD are both LOW, the interface parallel or serial output bus is enabled.

32

CS

DI

Chip Select. When CS and RD are both LOW, the interface parallel or serial output bus is enabled. CS is

also used to gate the external clock.

33

RESET

DI

Reset Input. When set to a logic HIGH, reset the AD7678. Current conversion, if any, is aborted. If not

used, this pin could be tied to DGND.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7679ACPZ | IC ADC 18BIT SAR W/BUFF 48LFCSP |

| AD7680BRM | IC ADC 16BIT LP UNIPOLAR 8-MSOP |

| AD7683BCPZRL7 | IC ADC 16BIT 100KSPS 8LFCSP |

| AD7684BRMZRL7 | IC ADC 16BIT 100KSPS DIFF 8MSOP |

| AD7685CCPZRL | IC ADC 16BIT SAR 250KSPS 10LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7678ACPZRL | 功能描述:IC ADC 18BIT SAR W/BUFF 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:PulSAR® 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD7678AST | 制造商:Analog Devices 功能描述:ADC Single SAR 100ksps 18-bit Parallel/Serial 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:18-BIT, 100KSPS SAR ADC - Bulk 制造商:Analog Devices 功能描述:18BIT SAR ADC SMD 7678 LQFP48 |

| AD7678ASTRL | 制造商:Analog Devices 功能描述:ADC Single SAR 100ksps 18-bit Parallel/Serial 48-Pin LQFP T/R 制造商:Analog Devices 功能描述:ADC SGL SAR 100KSPS 18BIT PARALLEL/SERL 48LQFP - Tape and Reel |

| AD7678ASTZ | 功能描述:IC ADC 18BIT SAR 100KSPS 48-LQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:PulSAR® 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD7678ASTZ | 制造商:Analog Devices 功能描述:18BIT SAR ADC SMD 7678 LQFP48 |

发布紧急采购,3分钟左右您将得到回复。