- 您现在的位置:买卖IC网 > PDF目录10169 > AD7701ARZ-REEL (Analog Devices Inc)IC ADC 16BIT LC2MOS 20SOIC PDF资料下载

参数资料

| 型号: | AD7701ARZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/20页 |

| 文件大小: | 0K |

| 描述: | IC ADC 16BIT LC2MOS 20SOIC |

| 标准包装: | 1,000 |

| 位数: | 16 |

| 采样率(每秒): | 4k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 37mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 20-SOIC W |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 1 个单端,单极;1 个单端,双极 |

REV. E

–14–

AD7701

AGND

AD7701

AVDD

VREF

10k

0.1F

DVDD

DGND

AVSS

DVSS

0.1F

REF

AD707

0.1F

10V

1V

Figure 17. Single-Supply Operation

SLEEP MODE

The low power standby mode is initiated by taking the

SLEEP

input low, which shuts down all analog and digital circuits and

reduces power consumption to 10

W. The calibration coeffi-

cients are still retained in memory, but as the converter has been

quiescent, it is necessary to wait for the filter settling time (507,904

cycles) before accessing the output data.

DIGITAL INTERFACE

The AD7701’s serial communications port allows easy inter-

facing to industry-standard microprocessors. Three different

modes of operations are available, optimized for different types

of interface.

Synchronous Self-Clocking Mode (SSC)

The SSC mode (MODE pin high) allows easy interfacing to

serial-parallel conversion circuits in systems with parallel data

communication. This mode allows interfacing to 74XX299

universal shift registers without any additional decoding. The

SSC mode can also be used with microprocessors such as the

68HC11 and 68HC05, which allow an external device to clock

their serial port.

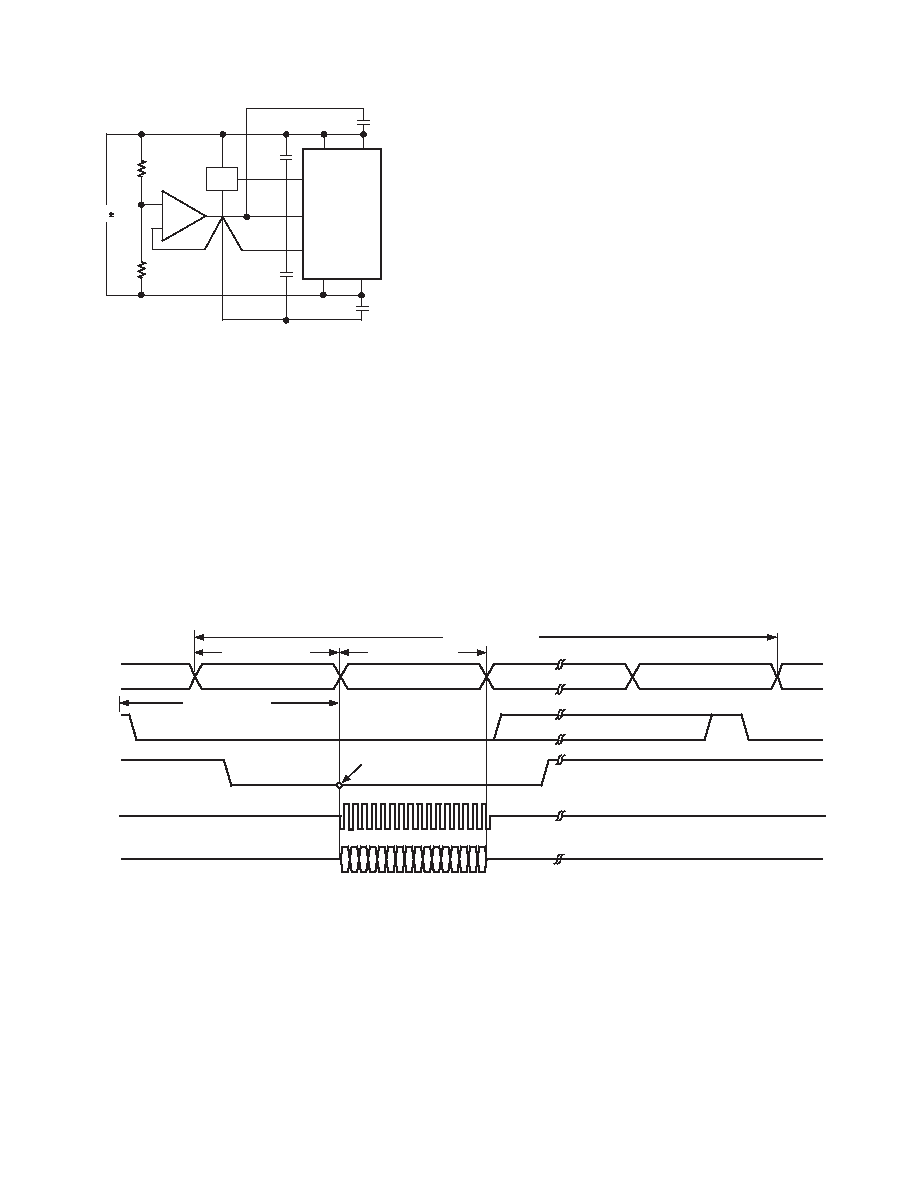

Figure 18 shows the timing diagram for SSC mode. Data is

clocked out by an internally generated serial clock. The AD7701

divides each sampling interval into 16 distinct periods. Eight

periods of 64 clock pulses are for analog settling and eight peri-

ods of 64 clock pulses are for digital computation. The status of

CS is polled at the beginning of each digital computation period. If

it is low at any of these times, SCLK will become active and the

data-word currently in the output register will be transmitted,

MSB first. After the LSB has been transmitted,

DRDY goes

high and SDATA goes three-state. If

CS, having been brought

low, is taken high again at any time during data transmission,

SDATA and SCLK will go three-state after the current bit

finishes. If

CS is subsequently brought low, transmission will

resume with the next bit during the subsequent digital computa-

tion period. If transmission has not been initiated and completed

by the time the next data-word is available,

DRDY will go high

for four clock cycles then low again as the new word is loaded

into the output register.

A more detailed diagram of the data transmission in the SSC

mode is shown in Figure 19. Data bits change on the falling

edge of SCLK and are valid on the rising edge of SCLK.

ANALOG SETTLING

DIGITAL COMPUTATION

SCLK (O)

SDATA (O)

HI-Z

MSB

LSB

DRDY (O)

DIGITAL COMPUTATION

CS POLLED

CS (I)

INTERNAL

STATUS

72 CLKIN CYCLES

64 CLKIN CYCLES

1024 CLKIN CYCLES

64 CLKIN CYCLES

Figure 18. Timing Diagram for SSC Data Transmission Mode

相关PDF资料 |

PDF描述 |

|---|---|

| VI-264-CU-F3 | CONVERTER MOD DC/DC 48V 200W |

| VI-27Z-MX | CONVERTER MOD DC/DC 2V 30W |

| ADM207ARZ-REEL | IC TXRX RS232 5DVR/3REC 24SOIC |

| SF4382-3FPG-3ES | CONN RCPT 3POS PNL MNT PIN |

| IDT7208L25J | IC FIFO 64KX9 25NS 32PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7701BN | 功能描述:IC ADC 16BIT LC2MOS MONO 20-DIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD7701BNZ | 功能描述:IC ADC 16BIT LC2MOS MONO 20-DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD7701BQ | 制造商:AD 制造商全称:Analog Devices 功能描述:LC2MOS 16-Bit A/D Converter |

| AD7701BR | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 4ksps 16-bit Serial 20-Pin SOIC W 制造商:Rochester Electronics LLC 功能描述:16 BIT SIGMA DELTA CONVER - Bulk |

| AD7701BR-REEL | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。