- 您现在的位置:买卖IC网 > PDF目录10667 > AD7767BRUZ (Analog Devices Inc)ADC 24BIT 128KSPS SAR 16-TSSOP PDF资料下载

参数资料

| 型号: | AD7767BRUZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/25页 |

| 文件大小: | 0K |

| 描述: | ADC 24BIT 128KSPS SAR 16-TSSOP |

| 标准包装: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 128k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 18mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 管件 |

| 输入数目和类型: | 1 个差分,单极 |

| 产品目录页面: | 779 (CN2011-ZH PDF) |

| 配用: | EVAL-AD7767EDZ-ND - BOARD EVAL AD7767 128KSPS 108DB EVAL-AD7767-1EDZ-ND - BOARD EVAL AD7767-1 64KSPS 111DB |

AD7767

Rev. C | Page 17 of

24

AD7767 INTERFACE

The AD7767 provides the user with a flexible serial interface,

enabling the user to implement the most desirable interfacing

scheme for their application. The AD7767 interface comprises

seven different signals. Five of these signals are inputs: MCLK,

CS, SYNC/PD, SCLK, and SDI. The other two signals are

outputs: DRDY and SDO.

INITIAL POWER-UP

On initial power-up, apply a continuous MCLK signal. It is

recommended that the user reset the AD7767 to clear the filters

and ensure correct operation. The reset is completed as shown

in Figure 5, with all events occurring relative to the rising edge

of MCLK. A negative pulse on the SYNC/PD input initiates the

reset, and the DRDY output switches to logic high and remains

high until valid data is available. Following the power-up of the

AD7767 by transitioning the SYNC/PD pin to logic high, a settling

time is required before valid data is output by the device. This

settling time, tSETTLING, is a function of the MCLK frequency and

the decimation rate.

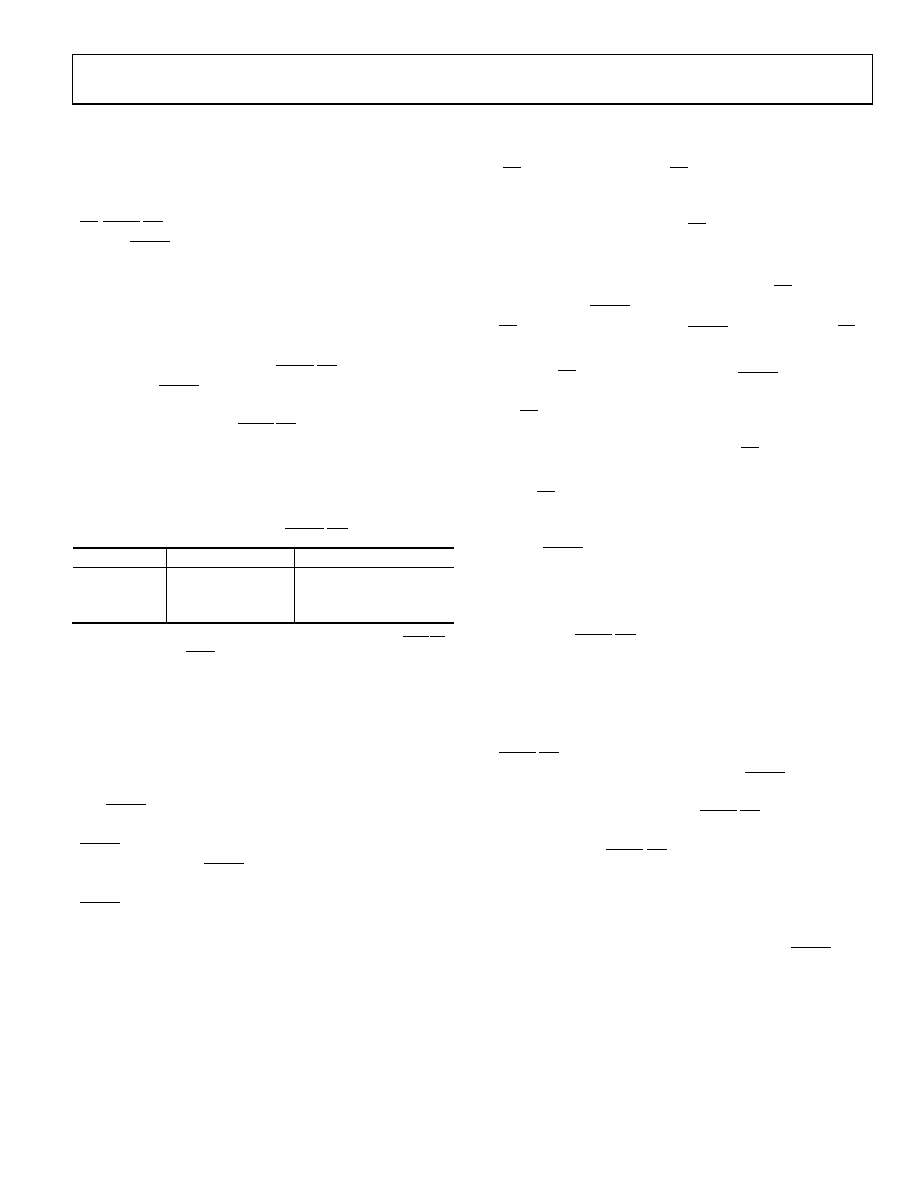

lists the settling time of each AD7767

model and should be referenced when reviewing

Table 7. Filter Settling Time After SYNC/PD

Model

Decimation Rate

tSETTLING1

AD7767

8

(594 × tMCLK) + t21

AD7767-1

16

(1186 × tMCLK) + t21

AD7767-2

32

(2370 × tMCLK) + t21

1 tSETTLING is measured from the first MCLK rising edge after the rising edge of SYNC/PD

to the falling edge of DRDY.

READING DATA

The AD7767 outputs its data conversion results in an MSB-first,

twos complement, 24-bit format on the serial data output pin

(SDO). MCLK is the master clock, which controls all the AD7767

conversions. The SCLK is the serial clock input for the device.

All data transfers take place with respect to the SCLK signal.

The DRDY line is used as a status signal to indicate when the

data is available to be read from the AD7767. The falling edge of

DRDY indicates that a new data-word is available in the output

register of the device. DRDY stays low during the period that

output data is permitted to be read from the SDO pin. The

DRDY signal returns to logic high to indicate when not to read

from the device. Ensure that a data read is not attempted during

this period while the output register is being updated.

The AD7767 offers the option of using a chip select input signal

(CS) in its data read cycle. The CS signal is a gate for the SDO pin

and allows many AD7767 devices to share the same serial bus. It

acts as an instruction signal to each of these devices indicating

permission to use the bus. When CS is logic high, the SDO line

of the AD7767 is tristated.

There are two distinct patterns that can be initiated to read data

from the AD7767 device: a pattern for when the CS falling edge

occurs after the DRDY falling edge and a pattern for when the

CS falling edge occurs before the DRDY falling edge (when CS

is set to logic low).

When the CS falling edge occurs after the DRDY falling edge,

the MSB of the conversion result is available on the SDO line on

the CS falling edge. The remaining bits of the conversion result

(MSB 1, MSB 2, and so on) are clocked onto the SDO line

by the falling edges of SCLK that follow the CS falling edge.

details this interfacing scheme.

When CS is tied low, the AD7767 serial interface can operate in

3-wire mode as shown in

. In this case, the MSB of the

conversion result is available on the SDO line on the falling

edge of

DRDY. The remaining bits of the data conversion result

(MSB 1, MSB 2, and so on) are clocked onto the SDO line

by the subsequent SCLK falling edges.

POWER-DOWN, RESET, AND SYNCHRONIZATION

The AD7767 SYNC/PD pin allows the user to synchronize

multiple AD7767 devices. This pin also allows the user to reset

and power down the AD7767 device. These features are

implemented relative to the rising edges of MCLK and are

shown in

, marked as A, B, C, and D.

To power down, reset, or synchronize a device, the AD7767

SYNC/PD pin should be taken low. On the first rising edge of

MCLK, the AD7767 is powered down. The DRDY pin transi-

tions to logic high, indicating that the data in the output register

is no longer valid. The status of the SYNC/PD pin is checked on

each subsequent rising edge of MCLK. On the first rising edge

of MCLK after the SYNC/PD pin is taken high, the AD7767 is

taken out of power-down. On the next rising edge, the filter of

the AD7767 is reset. On the following rising edge, the first new

sample is taken.

A settling time, tSETTLING, from the filter reset must elapse before

valid data is output by the device (see Table 7). The DRDY

output goes logic low after tSETTLING to indicate when valid data is

available on SDO for readback.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7660ASTZ | IC ADC 16BIT UNIPOLAR 48-LQFP |

| VE-J11-MW-F1 | CONVERTER MOD DC/DC 12V 100W |

| LTC1403AIMSE#PBF | IC ADC 14BIT 2.8MSPS 10-MSOP |

| AD7658BSTZ | IC ADC 12BIT 6CH 250KSPS 64LQFP |

| AD7767BRUZ-1 | ADC 24BIT 64KSPS SAR 16-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7767BRUZ-1 | 功能描述:ADC 24BIT 64KSPS SAR 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6 |

| AD7767BRUZ-1-RL7 | 功能描述:ADC 24BIT 10.5MW 64KSPS 16TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7767BRUZ-2 | 功能描述:ADC 24BIT 32KSPS SAR 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD7767BRUZ-2-RL7 | 功能描述:ADC 24BIT 8.5MW 32KSPS 16TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7767BRUZ-RL7 | 功能描述:ADC 24BIT 15MW 128KSPS 16TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

发布紧急采购,3分钟左右您将得到回复。