参数资料

| 型号: | AD8004SQ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/17页 |

| 文件大小: | 0K |

| 描述: | IC OPAMP CF QUAD LP LDIST 14CDIP |

| 标准包装: | 25 |

| 放大器类型: | 电流反馈 |

| 电路数: | 4 |

| 转换速率: | 3000 V/µs |

| -3db带宽: | 250MHz |

| 电流 - 输入偏压: | 40µA |

| 电压 - 输入偏移: | 1000µV |

| 电流 - 电源: | 14mA |

| 电流 - 输出 / 通道: | 50mA |

| 电压 - 电源,单路/双路(±): | 4 V ~ 12 V,±2 V ~ 6 V |

| 工作温度: | -55°C ~ 125°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 14-CDIP(0.300",7.62mm) |

| 供应商设备封装: | 14-CERDIP |

| 包装: | 管件 |

REV. C

AD8004

–10–

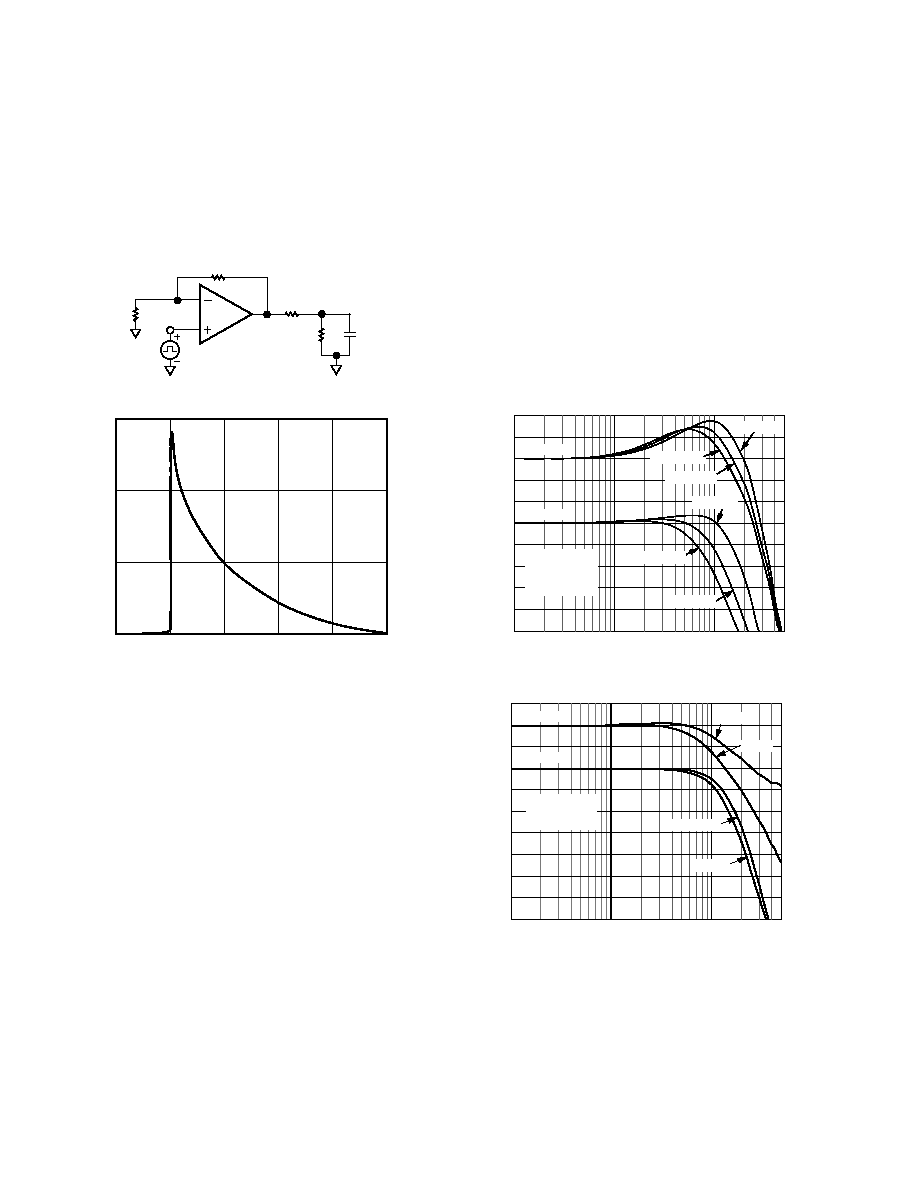

DRIVING CAPACITIVE LOADS

The AD8004 was designed primarily to drive nonreactive loads.

If driving loads with a capacitive component is desired, best

settling response is obtained by the addition of a small series

resistance as shown in Figure 6. The accompanying graph shows

the optimum value for RSERIES vs. capacitive load. It is worth

noting that the frequency response of the circuit when driving

large capacitive loads will be dominated by the passive roll-off of

RSERIES and CL.

1k

RL

1k

CL

AD8004

RSERIES

1k

Figure 6. Driving Capacitive Load

40

30

20

010

15

20

25

CL – pF

10

R

SERIES

–

5

Figure 7. Recommended RSERIES vs. Capacitive Load for

30 ns Settling to 0.1%

OPTIMIZING FLATNESS

The fine scale gain flatness and –3 dB bandwidth is affected by

RFEEDBACK selection as is normal of current feedback amplifiers.

With the exception of gain = +1, the AD8004 can be adjusted

for either maximal flatness with modest closed-loop bandwidth

or for mildly peaked-up frequency response with much more

bandwidth. Figure 8 shows the effect of three evenly spaced RF

changes upon gain = +1 and gain = +2. Table I shows the

recommended component values for achieving maximally flat

frequency response as well as a faster slightly peaked-up fre-

quency response.

Printed circuit board parasitics and device lead frame parasitics

also control fine scale gain flatness. The AD8004R package,

because of its small lead frame, offers superior parasitics relative

to the N package. In the printed circuit board environment,

parasitics such as extra capacitance caused by two parallel and

vertical flat conductors on opposite PC board sides in the

region of the summing junction will cause some bandwidth

extension and/or increased peaking. In noninverting gains, the

effect of extra capacitance on summing junctions is far more

pronounced than with inverting gains. Figure 9 shows an example

of this. Note that only 1 pF of added junction capacitance causes

about a 70% bandwidth extension and additional peaking on a

gain = +2. For an inverting gain = –2, 5 pF of additional summing

junction capacitance caused a small 10% bandwidth extension.

Extra output capacitive loading also causes bandwidth exten-

sions and peaking. The effect is more pronounced with less

resistive loading from the next stage. Figure 10 shows the effect

of direct output capacitive loads for gains of +2 and –2. For both

gains CLOAD was set to 10 pF or 0 pF (no extra capacitive loading).

For each of the four traces in Figure 10 the resistive loads were

100

. Figure 11 also shows capacitive loading effects with a

lighter output resistive load. Note that even though bandwidth

is extended 2

, the flatness dramatically suffers.

FREQUENCY – MHz

–2

1

500

10

40

100

1

0

–1

VIN = 50mV rms

VS = 5V

RL = 100

R PACKAGE

–3

–4

–5

NORMALIZED

GAIN

–

dB,

G

=

+2

2

–3

0

1

–1

–2

–4

–5

–6

RF = 1.10k

RF = 604

G = +1

G = +2

–7

–8

GAIN

–

dB,

G

=

+1

RF = 845

RF = 909

RF = 1.1k

RF = 698

Figure 8. RFEEDBACK vs. Frequency Response, G = +1/+2

FREQUENCY – MHz

2

–8

1

500

10

40

100

–2

0

–4

–6

VIN = 50mV rms

RL = 100

5VS

–10

–12

–14

NORMALIZED

GAIN

–

dB,

G

=

–2

NORMALIZED

GAIN

–

dB,

G

=

+2

2

–8

–2

0

–4

–6

–10

–12

–14

CJ = 1pF

CJ = 0

CJ = 5.1pF

CJ = 0

G = +2

G = –2

Figure 9. Frequency Response vs. Added Summing

Junction Capacitance

相关PDF资料 |

PDF描述 |

|---|---|

| AD8005ARZ-REEL7 | IC OPAMP CF ULP LDIST 10MA 8SOIC |

| AD8008ARZ-REEL | IC OPAMP CF DUAL ULDIST LN 8SOIC |

| AD8010ARZ-16 | IC OPAMP CF 200MA LP 16SOIC |

| AD8011ARZ-REEL | IC OPAMP CF LP LDIST 30MA 8SOIC |

| AD8012ARZ-REEL7 | IC OPAMP CF DUAL LP 125MA 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8005 | 制造商:AD 制造商全称:Analog Devices 功能描述:270 MHz, 400 uA Current Feedback Amplifier |

| AD80052AKBCRL-45 | 制造商:Analog Devices 功能描述: |

| AD80052BR | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD800-52BR | 功能描述:IC CLK\DATA RECOVERY PLL 20-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| AD800-52BRRL | 功能描述:IC CLK\DATA RECOVERY PLL 20-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。