- 您现在的位置:买卖IC网 > PDF目录1893 > AD8197BASTZ-RL (Analog Devices Inc)IC SWITCH DVI/HDMI 4:1 100-LQFP PDF资料下载

参数资料

| 型号: | AD8197BASTZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/28页 |

| 文件大小: | 0K |

| 描述: | IC SWITCH DVI/HDMI 4:1 100-LQFP |

| 标准包装: | 1,000 |

| 功能: | 开关 |

| 电路: | 1 x 16:1 |

| 电压电源: | 单电源 |

| 电压 - 电源,单路/双路(±): | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-LQFP(14x14) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD8197B

Rev. 0 | Page 19 of 28

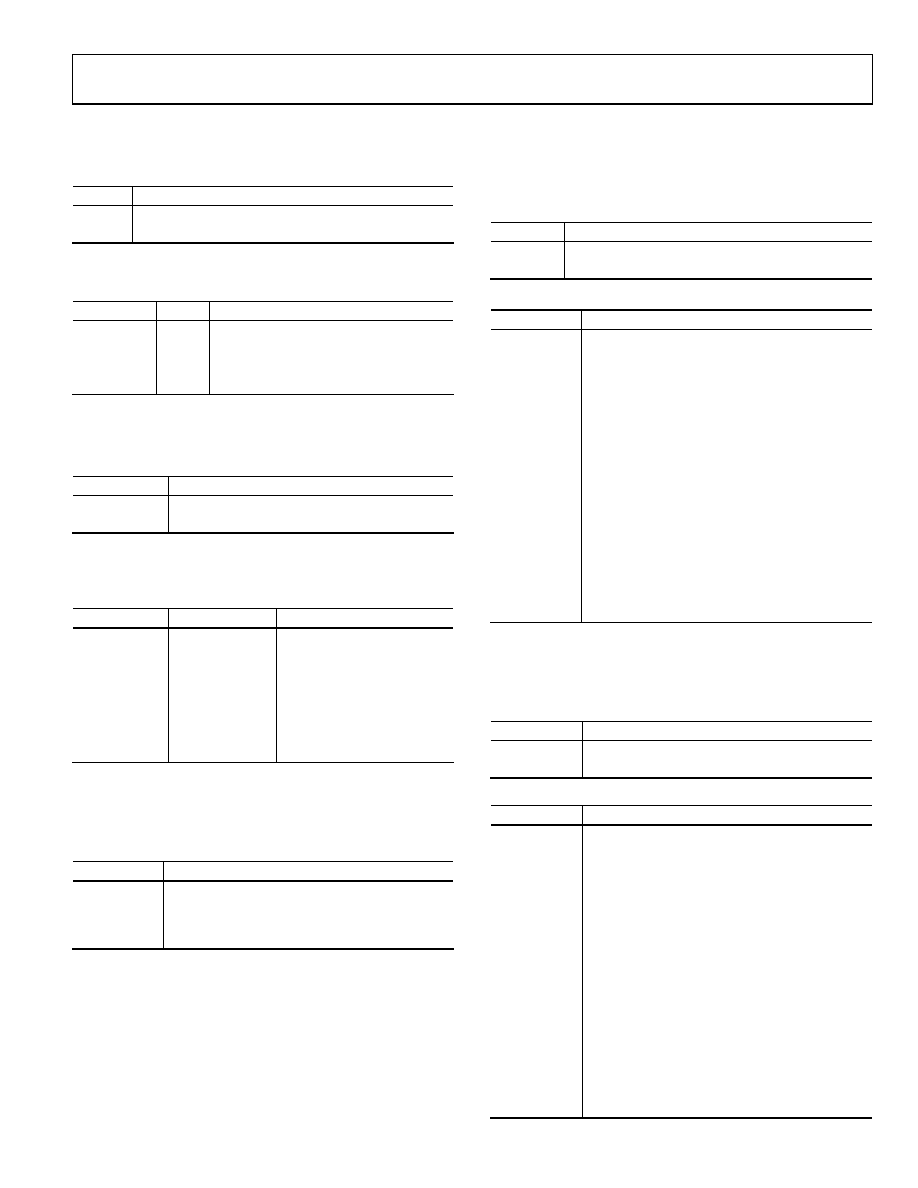

HIGH SPEED DEVICE MODES REGISTER

HS_EN: High Speed (TMDS) Channels Enable Bit

Table 6. HS_EN Description

HS_EN

Description

0

High speed channels off, low power/standby mode

1

High speed channels on

HS_CH[1:0]: High Speed (TMDS) Switch Source Select Bus

Table 7. HS_CH Mapping

HS_CH[1:0]

O[3:0]

Description

00

A[3:0]

High Speed Source A switched to output

01

B[3:0]

High Speed Source B switched to output

10

C[3:0]

High Speed Source C switched to output

11

D[3:0]

High Speed Source D switched to output

AUXILIARY DEVICE MODES REGISTER

AUX_EN: Auxiliary (Low Speed) Switch Enable Bit

Table 8. AUX_EN Description

AUX_EN

Description

0

Auxiliary switch off

1

Auxiliary switch on

AUX_CH[1:0]: Auxiliary (Low Speed) Switch Source

Select Bus

Table 9. AUX_CH Mapping

AUX_CH[3:0]

AUX_COM[3:0]

Description

00

AUX_A[3:0]

Auxiliary Source A switched

to output

01

AUX_B[3:0]

Auxiliary Source B switched

to output

10

AUX_C[3:0]

Auxiliary Source C switched

to output

11

AUX_D[3:0]

Auxiliary Source D switched

to output

RECEIVER SETTINGS REGISTER

RX_TS: High Speed (TMDS) Channels Input Termination

On/Off Select Bit

Table 10. RX_TS Description

RX_TS

Description

0

All input terminations off (switches open)

1

Input termination resistor switch is controlled by

RX_TO[x] control bits from Input Term. Resistor

Control Registers 1 and 2.

INPUT TERMINATION SELECT REGISTER 1 AND

REGISTER 2

RX_TO[X]: High Speed (TMDS) Input Channel X

Termination Select Bit

Table 11. RX_TO[X] Description

RX_TO[X]

Description

0

Input termination for TMDS Channel X disconnected

1

Input termination for TMDS Channel X connected

Table 12. RX_TO[X] Mapping

RX_TO[X]

Corresponding Input TMDS Channel

Bit 0

B0

Bit 1

B1

Bit 2

B2

Bit 3

B3

Bit 4

A0

Bit 5

A1

Bit 6

A2

Bit 7

A3

Bit 8

C3

Bit 9

C2

Bit 10

C1

Bit 11

C0

Bit 12

D3

Bit 13

D2

Bit 14

D1

Bit 15

D0

RECEIVE EQUALIZER REGISTER 1 AND REGISTER 2

RX_EQ[X]: High Speed (TMDS) Input X Equalization Level

Select Bit

Table 13. RX_EQ[X] Description

RX_EQ[X]

Description

0

Low equalization (6 dB)

1

High equalization (12 dB)

Table 14. RX_EQ[X] Mapping

RX_EQ[X]

Corresponding Input TMDS Channel

Bit 0

B0

Bit 1

B1

Bit 2

B2

Bit 3

B3

Bit 4

A0

Bit 5

A1

Bit 6

A2

Bit 7

A3

Bit 8

C3

Bit 9

C2

Bit 10

C1

Bit 11

C0

Bit 12

D3

Bit 13

D2

Bit 14

D1

Bit 15

D0

相关PDF资料 |

PDF描述 |

|---|---|

| AD8303ARZ-REEL | IC DAC 12BIT SERIAL 14SOIC |

| AD8391AR-REEL7 | IC XDSL LINE DVR W/PWR DN 8-SOIC |

| AD8392AAREZ | IC ADSL/ADSL2 LINE DRVR 28-TSSOP |

| AD8394AREZ-R7 | IC OPAMP ADSL/ADSL2 DL 20TSSOP |

| AD8396ACPZ-RL | IC LINE DRVR ADSL/ADSL2 16LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8197BASTZ-RLKL1 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD8197B-EVALZ | 制造商:Analog Devices 功能描述:EVAL KIT FOR 4:1 HDMI/DVI SWIT W/ EQUALIZATION - Bulk |

| AD8197B-XSTZ | 功能描述:IC SWITCH DVI/HDMI 4:1 100-LQFP 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:上次购买时间 类型:视频开关 应用:HDTV,投影仪,机顶盒 安装类型:表面贴装 封装/外壳:100-LQFP 供应商器件封装:100-LQFP(14x14) 标准包装:1 |

| AD8197-EVAL | 制造商:Analog Devices 功能描述:EVAL KIT FOR 4:1 HDMI/DVI SWIT W/ EQUALIZATION 100LQFP - Bulk |

| AD820 | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。