- 您现在的位置:买卖IC网 > PDF目录373944 > AD8345ARE-REEL (ANALOG DEVICES INC) 250 MHz.1000 MHz Quadrature Modulator PDF资料下载

参数资料

| 型号: | AD8345ARE-REEL |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 衰减器 |

| 英文描述: | 250 MHz.1000 MHz Quadrature Modulator |

| 中文描述: | 140 MHz - 1000 MHz RF/MICROWAVE QUADRAPHASE MODULATOR |

| 封装: | MO-153ABT, TSSOP-16 |

| 文件页数: | 9/16页 |

| 文件大小: | 372K |

| 代理商: | AD8345ARE-REEL |

REV. 0

AD8345

–9–

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

AD8345

QBBP

QBBN

COM3

COM3

VPS2

VOUT

COM2

COM3

IBBP

IBBN

COM3

COM1

LOIN

LOIP

VPS1

ENBL

IP

1

T1

ETC1-1-13

2

3

4

5

LO

R1

50

C6

1000pF

C7

1000pF

IN

C3

1000pF

C4

+V

S

QP

QN

C1

1000pF

C2

0.01 F

+V

S

VOUT

C5

1000pF

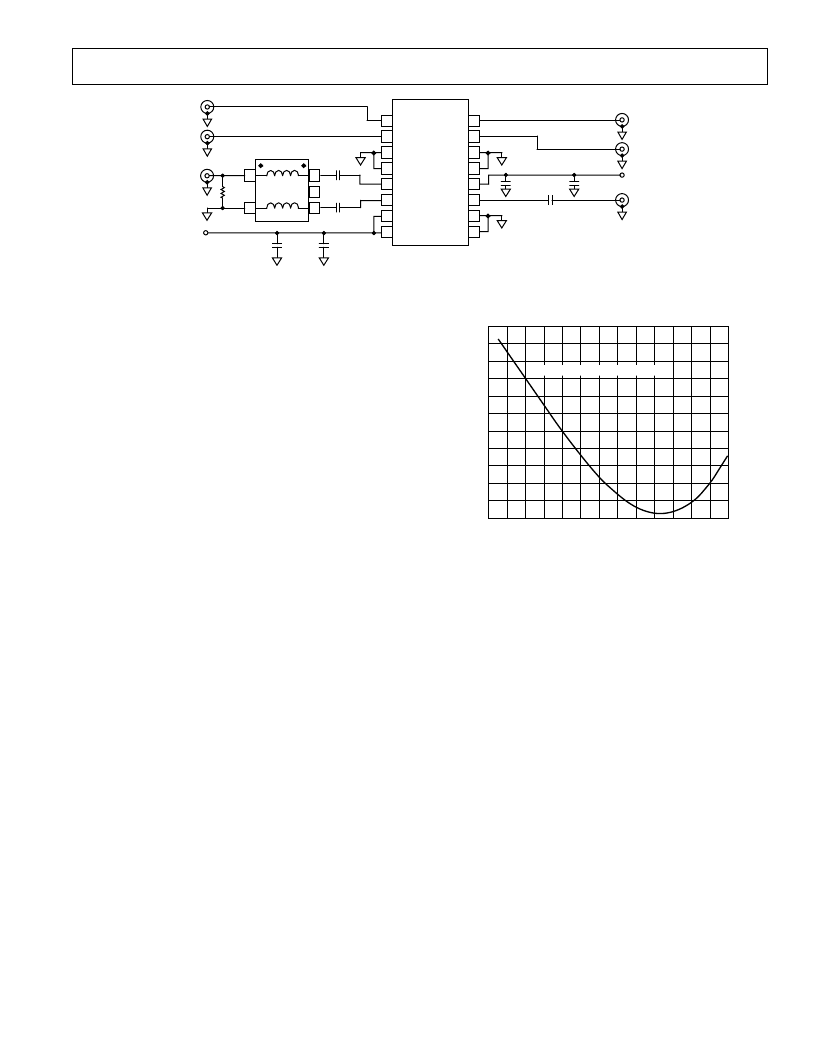

Figure 3. Basic Connections

LO FREQUENCY

–

MHz

40

S

–

–

60

60

80

100 120 140 160 180 200 220 240 260 280 300

–

55

–

50

–

45

–

40

–

35

–

30

–

25

–

20

–

15

–

10

–

5

V

S

= 5V, DIFFERENTIAL INPUT = 1.2V

Figure 4. Typical Lower Frequency Sideband Suppression

Performance

Baseband I and Q Channel Drive

The I and Q channel baseband inputs should be driven differen-

tially. This is convenient as most modern high-speed DACs

have differential outputs. For optimal performance at V

S

= 5 V,

the drive signal should be a 1.2 V p-p differential signal with a

bias level of 0.7 V; that is, each input should swing from 0.4 V

to 1 V. If the AD8345 is being run on a lower supply voltage,

the peak-to-peak voltage on the I and Q channel inputs must be

reduced to avoid input clipping. For example, at a supply volt-

age of 2.7 V, a 200 mV p-p differential drive is recommended.

This will result in a corresponding reduction in output power

(see TPC 1). The I and Q inputs have a large input bandwidth

of approximately 80 MHz. At lower baseband input levels, the

input bandwidth increases (see TPC 2).

If the baseband signal has a high peak-to-average ratio (e.g.,

CDMA or WCDMA), the rms signal strength will have to be

backed off from this peak level in order to prevent clipping of

the signal peaks. Clipping of signal peaks will tend to increase

signal leakage into adjacent channels. Backing off the I and Q

signal strength in the manner recommended will reduce the output

power by a corresponding amount. This also applies to multicarrier

applications where the per-carrier output power will be lower by

3 dB for each doubling of the number of output carriers.

BASIC CONNECTIONS

The basic connections for operating the AD8345 are shown in

Figure 3. A single power supply of between 2.7 V and 5.5 V is

applied to pins VPS1 and VPS2. A pair of ESD protection diodes

are connected internally between VPS1 and VPS2 so these must

be tied to the same potential. Both pins should be individually

decoupled using 1000 pF and 0.01

μ

F capacitors, located as

close as possible to the device. For normal operation, the enable

pin, ENBL, must be pulled high. The turn-on threshold for

ENBL is V

S

/2. Pins COM1 to COM3 should all be tied to the

same low impedance ground plane.

LO Drive

In Figure 3, a 50

resistor to ground combines with the device’s

high input impedance to provide an overall input impedance of

approximately 50

(see TPC 17 for a plot of LO port input

impedance). For maximum LO suppression at the output, a

differential LO drive is recommended. In Figure 3, this is

achieved using a balun (M/A-COM Part Number ETC1-1-13).

The output of the balun is ac coupled to the LO inputs which

have a bias level about 1.8 V dc. An LO drive level of –2 dBm is

recommended for lowest output noise. Higher levels will degrade

linearity while lower levels will tend to increase the noise floor

slightly. For example, reducing the LO power from –2 dBm to

–10 dBm will increase the noise floor by approximately 0.3 dB

(see TPC 19).

The LO terminal can be driven single-ended at the expense of

slightly higher LO leakage. LOIN is ac coupled to ground using

a capacitor and LOIP is driven through a coupling capacitor

from a (single-ended) 50

source (this scheme could also be

reversed with the drive signal being applied to LOIN).

LO Frequency Range

The frequency range on the LO input is limited by the internal

quadrature phase splitter. The phase splitter generates drive

signals for the internal mixers which are 90

°

out of phase relative

to one another. Outside of the specified LO frequency range of

250 MHz to 1 GHz, this quadrature accuracy degrades, result-

ing in decreased sideband suppression. See TPC 9 for a plot of

sideband suppression vs. LO frequency from 250 MHz to 1GHz.

Figure 4 shows the sideband suppression of a typical device

from 50 MHz to 300 MHz. The level of sideband suppression

degradation below 250 MHz will be subject to manufacturing

process variations.

相关PDF资料 |

PDF描述 |

|---|---|

| AD8345ARE-REEL7 | 250 MHz.1000 MHz Quadrature Modulator |

| AD8345 | 250 MHz.1000 MHz Quadrature Modulator |

| AD8345-EVAL | 250 MHz.1000 MHz Quadrature Modulator |

| AD8345ARE | 250 MHz.1000 MHz Quadrature Modulator |

| AD8346ARU-REEL | 0.8 GHz-2.5 GHz Quadrature Modulator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8345ARE-REEL7 | 功能描述:IC QUADRATURE MOD 250MHZ 16TSSOP RoHS:否 类别:RF/IF 和 RFID >> RF 调制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 功能:调制器 LO 频率:700MHz ~ 2.3GHz RF 频率:700MHz ~ 2.3GHz P1dB:1dBm 底噪:-148dBm/Hz 输出功率:-1dBm 电流 - 电源:46mA 电源电压:2.7 V ~ 3.6 V 测试频率:1.75GHz 封装/外壳:28-WFQFN 裸露焊盘 包装:带卷 (TR) |

| AD8345AREZ | 功能描述:IC QUADRATURE MOD 250MHZ 16TSSOP RoHS:是 类别:RF/IF 和 RFID >> RF 调制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 功能:调制器 LO 频率:700MHz ~ 2.3GHz RF 频率:700MHz ~ 2.3GHz P1dB:1dBm 底噪:-148dBm/Hz 输出功率:-1dBm 电流 - 电源:46mA 电源电压:2.7 V ~ 3.6 V 测试频率:1.75GHz 封装/外壳:28-WFQFN 裸露焊盘 包装:带卷 (TR) |

| AD8345AREZ | 制造商:Analog Devices 功能描述:IC QUAD MODULATOR 140MHZ-1GHZ 16-TSSO 制造商:Analog Devices 功能描述:IC, QUAD MODULATOR, 140MHZ-1GHZ, 16-TSSO |

| AD8345AREZ-REEL | 制造商:Analog Devices 功能描述:Quadrature Mod 80MHz 16-Pin TSSOP EP T/R |

| AD8345AREZ-RL7 | 功能描述:IC MOD QUAD 300-1000MHZ 16TSSOP RoHS:是 类别:RF/IF 和 RFID >> RF 调制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 功能:调制器 LO 频率:700MHz ~ 2.3GHz RF 频率:700MHz ~ 2.3GHz P1dB:1dBm 底噪:-148dBm/Hz 输出功率:-1dBm 电流 - 电源:46mA 电源电压:2.7 V ~ 3.6 V 测试频率:1.75GHz 封装/外壳:28-WFQFN 裸露焊盘 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。