- 您现在的位置:买卖IC网 > PDF目录373956 > AD871 (Analog Devices, Inc.) Complete 12-Bit 5 MSPS Monolithic A/D Converter(12位5MSPS单片A/D转换器) PDF资料下载

参数资料

| 型号: | AD871 |

| 厂商: | Analog Devices, Inc. |

| 英文描述: | Complete 12-Bit 5 MSPS Monolithic A/D Converter(12位5MSPS单片A/D转换器) |

| 中文描述: | 完整的12位5 MSPS的单片的A / D转换器(12位5MSPS单片的A / D转换器) |

| 文件页数: | 15/16页 |

| 文件大小: | 319K |

| 代理商: | AD871 |

AD871

REV. A

–15–

1

2

V

INA

V

INB

AD871

V

IN

IBPO

IOUT

RL

ACOM

LCOM

REF COM

AD568

74

HC

574

74

HC

574

8

8

4

4

DIGITAL

OFFSET

WORD

Figure 32. Offset Correction Using the AD568

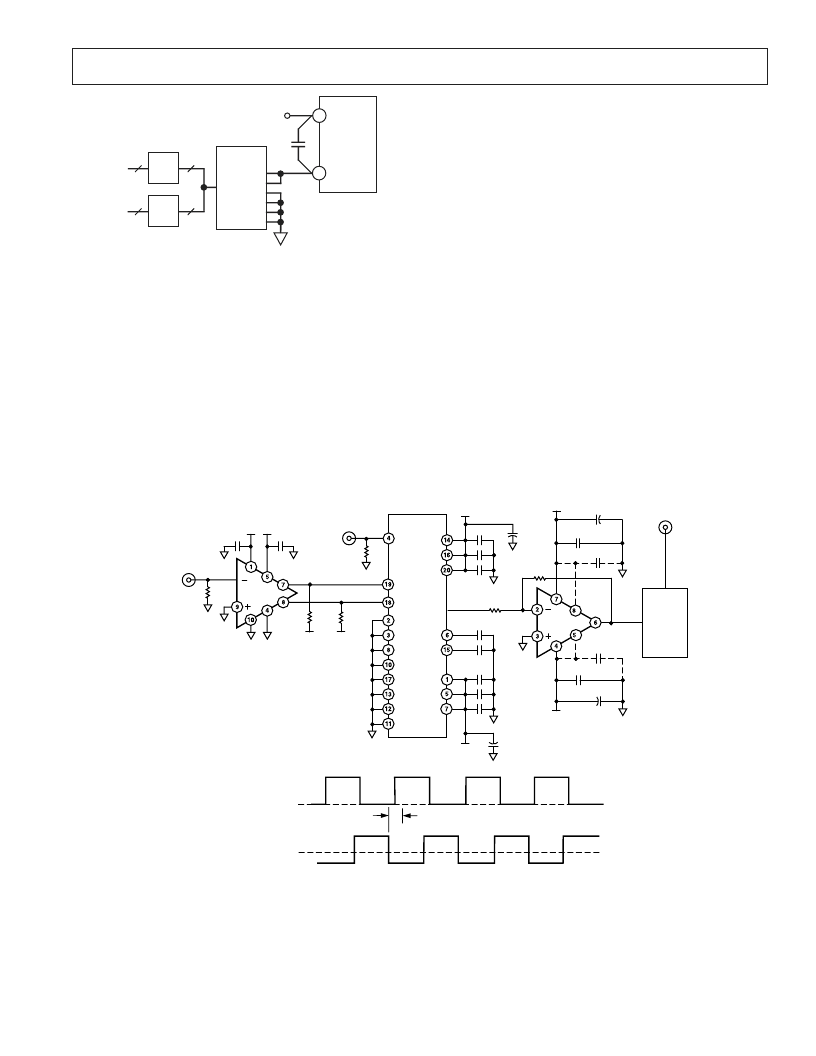

UNDERSAMPLING USING THE AD871 AND AD9100

The AD871’s on-chip THA optimizes transient response while

maintaining low noise performance. For super-Nyquist (under-

sampling) applications it may be necessary to use an external

THA with fast track-mode slew rate and hold mode settling

time. An excellent choice for this application is the AD9100, an

ultrahigh speed track-and-hold amplifier.

In order to maximize the spurious free dynamic range of the cir-

cuit in Figure 33, it is advantageous to present a small signal to

the input of the AD9100 and then amplify the output to the

AD871’s full-scale input range. This can be accomplished with

a low distortion, wide bandwidth amplifier such as the AD9617.

The circuit uses a gain of 3.5 to optimize S/(N+D).

The peak performance of this circuit is obtained by driving the

AD871 + AD9100 combination with a full-scale input. For

small scale input signals (–20 dB, –40 dB), the AD871 performs

better without the track-and-hold because slew-limiting effects

are no longer dominant. To gain the advantages of the added

track-and-hold, it is important to give the AD871 a full-scale

input.

An alternative to the configuration presented above is to use the

AD9101 track-and-hold amplifier. The AD9101 provides a

built-in post amplifier with a gain of 4, providing excellent ac

characteristics in conjunction with a high level of integration.

As illustrated in Figure 33, it is necessary to skew the AD871

sample clock and the AD9100 sample/hold control. Clock skew

(t

S

) is defined as the time starting at the AD9100’s transition

into hold mode and ending at the moment the AD871 samples.

The AD871 samples on the rising edge of the sample clock, and

the AD9100 samples on the falling edge of the sample/hold con-

trol. The choice of t

S

is primarily determined by the settling

time of the AD9100. The droop rate of the AD9100 must also

be taken into consideration. Using these values, the ideal t

S

is

17 ns. When choosing clock sources, it is extremely important

that the front end track-and-hold sample/hold control is given a

very low jitter clock source. This is not as crucial for the AD871

sample clock, because it is sampling a dc signal.

AD96685

R

T

CLOCK 1

IN

Q

Q

+V

S

–V

S

510

V

510

V

–V

S

R

T

V

IN

10

m

F

442

V

0.1

m

F

0.1

m

F

3.3

m

F

+5V

0.1

m

F

*

AD9617

*

0.1

m

F

3.3

m

F

–5V

10

m

F

–V

S

–V

S

+V

S

A

IN

AD871

EB

CLOCK 2

IN

*OPTIONAL, SEE

AD9617 DATA SHEET

+V

S

= 5.0V

–V

S

= –5.2V

ALL CAPACITORS ARE 0.01

m

F

(LOW INDUCTANCE - DECOUPLING)

UNLESS OTHERWISE NOTED.

0V

T = 200ns

+5V

+1V

–1V

T = 200ns

t

S

CLOCK 1

CLOCK 2

t

S

= 17ns

AD9100

127

V

Figure 33. Undersampling Using the AD871 and AD9100

相关PDF资料 |

PDF描述 |

|---|---|

| AD872A | Complete 12-Bit 10 MSPS Monolithic A/D Converter |

| AD872AJD | Complete 12-Bit 10 MSPS Monolithic A/D Converter |

| AD872AJE | Complete 12-Bit 10 MSPS Monolithic A/D Converter |

| AD872ASD | Complete 12-Bit 10 MSPS Monolithic A/D Converter |

| AD872ASE | Complete 12-Bit 10 MSPS Monolithic A/D Converter |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD871-EB | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| AD871JD | 制造商:Analog Devices 功能描述:ADC Single Pipelined 5Msps 12-bit Parallel 28-Pin SBCDIP 制造商:Rochester Electronics LLC 功能描述:IC, 12-BIT 5 MSPS ADC IC - Bulk |

| AD871JE | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 12-Bit 5 MSPS Monolithic A/D Converter |

| AD871SD | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述:IC, 12-BIT 5 MSPS ADC IC - Bulk |

| AD871SD/883B | 制造商:Rochester Electronics LLC 功能描述:IC, 12-BIT 5MSPS ADC IC - Bulk 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。