参数资料

| 型号: | AD8802ARZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/16页 |

| 文件大小: | 0K |

| 描述: | IC DAC 8BIT 12CH W/SD 20SOIC |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 37 |

| 系列: | TrimDAC® |

| 设置时间: | 600ns |

| 位数: | 8 |

| 数据接口: | 串行 |

| 转换器数目: | 12 |

| 电压电源: | 单电源 |

| 功率耗散(最大): | 60µW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 20-SOIC W |

| 包装: | 管件 |

| 输出数目和类型: | 12 电压,单极 |

| 采样率(每秒): | 1.7M |

AD8802/AD8804

REV. 0

–7–

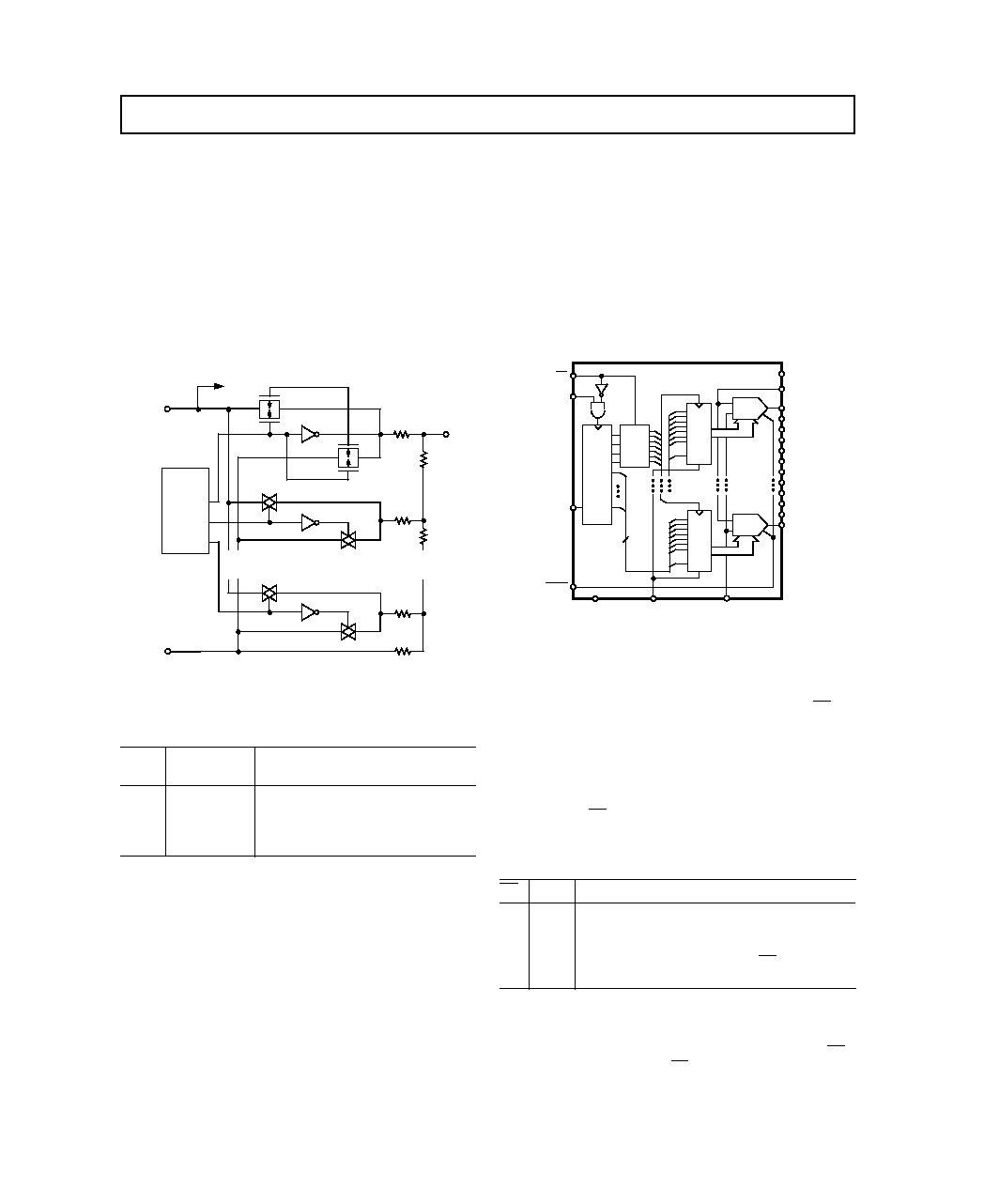

PROGRAMMING THE OUTPUT VOLTAGE

The output voltage range is determined by the external refer-

ence connected to VREFH and VREFL pins. See Figure 16 for a

simplified diagram of the equivalent DAC circuit. In the case of

the AD8802 its VREFL is internally connected to GND and

therefore cannot be offset. VREFH can be tied to VDD and VREFL

can be tied to GND establishing a basic rail-to-rail voltage out-

put programming range. Other output ranges are established by

the use of different external voltage references. The general

transfer equation which determines the programmed output

voltage is:

VO (Dx) = (Dx)/256

× (V

REFH – VREFL) + VREFL

Eq. 1

where Dx is the data contained in the 8-bit DACx register.

MSB

OX

2R

R

P CH

N CH

TO OTHER DACS

R

2R

GND

VREFL

LSB

DAC

REGISTER

D6

D0

D7

VREFH

......

...

Figure 16. AD8802/AD8804 Equivalent TrimDAC Circuit

For example, when VREFH = +5 V and VREFL = 0 V, the follow-

ing output voltages will be generated for the following codes:

Output State

D

VOx

(VREFH = +5 V, VREFL = 0 V)

255

4.98 V

Full Scale

128

2.50 V

Half Scale (Midscale Reset Value)

1

0.02 V

1 LSB

0

0.00 V

Zero Scale

REFERENCE INPUTS (VREFH, VREFL)

The reference input pins set the output voltage range of all

twelve DACs. In the case of the AD8802 only the VREFH pin is

available to establish a user designed full-scale output voltage.

The external reference voltage can be any value between 0 and

VDD but must not exceed the VDD supply voltage. The AD8804

has access to the VREFL which establishes the zero-scale output

voltage, any voltage can be applied between 0 V and VDD. VREFL

can be smaller or larger in voltage than VREFH since the DAC

design uses fully bidirectional switches as shown in Figure 16.

The input resistance to the DAC has a code dependent variation

which has a nominal worst case measured at 55H, which is ap-

proximately 1.2 k

. When V

REFH is greater than VREFL, the

REFL reference must be able to sink current out of the DAC

ladder, while the REFH reference is sourcing current into the

DAC ladder. The DAC design minimizes reference glitch cur-

rent maintaining minimum interference between DAC channels

during code changes.

DAC OUTPUTS (O1–O12)

The twelve DAC outputs present a constant output resistance of

approximately 5 k

independent of code setting. The distribu-

tion of ROUT from DAC-to-DAC typically matches within ± 1%.

However device-to-device matching is process lot dependent

having a

±20% variation. The change in R

OUT with temperature

has a 500 ppm/

°C temperature coefficient. During power shut-

down all twelve outputs are open-circuited.

CS

CLK

SDI

SHDN

AD8802/AD8804

D7

D0

ADDR

DEC

EN

D11

D10

D9

D8

D7

SER

REG

DD0

DAC

REG

#1

R

VDD

D7

D0

DAC

12

DAC

REG

#12

R

DAC

1

8

O1

O2

O4

O5

O6

O7

O8

O9

O10

O11

O12

VREFH

GND

RS

(AD8802 ONLY)

VREFL

(AD8804 ONLY)

O3

Figure 17. Block Diagram

DIGITAL INTERFACING

The AD8802/AD8804 contains a standard three-wire serial in-

put control interface. The three inputs are clock (CLK), CS and

serial data input (SDI). The positive-edge sensitive CLK input

requires clean transitions to avoid clocking incorrect data into

the serial input register. Standard logic families work well. If

mechanical switches are used for product evaluation, they

should be debounced by a flip-flop or other suitable means. Fig-

ure 17 block diagram shows more detail of the internal digital

circuitry. When CS is taken active low, the clock can load data

into the serial register on each positive clock edge, see Table II.

Table II. Input Logic Control Truth Table

CS

CLK

Register Activity

1

X

No effect.

0

P

Shifts Serial Register One bit loading the next bit

in from the SDI pin.

P

1

Clock should be high when the CS returns to the

inactive state.

P = Positive Edge, X = Don’t Care.

The data setup and data hold times in the specification table

determine the data valid time requirements. The last 12 bits of

the data word entered into the serial register are held when CS

returns high. At the same time CS goes high it gates the address

decoder which enables one of the twelve positive-edge triggered

DAC registers, see Figure 18 detail.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-JWZ-MW | CONVERTER MOD DC/DC 2V 40W |

| VI-JWY-MY | CONVERTER MOD DC/DC 3.3V 33W |

| LTC1446IN8 | IC D/A CONV 12BIT R-R DUAL 8-DIP |

| LTC1448IN8#PBF | IC DAC 12BIT R-R DUAL 8-DIP |

| VI-JWM-MY | CONVERTER MOD DC/DC 10V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8802ARZ-REEL | 功能描述:IC DAC 8BIT 12CH W/SD 20SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TrimDAC® 产品培训模块:LTC263x 12-, 10-, and 8-Bit VOUT DAC Family 特色产品:LTC2636 - Octal 12-/10-/8-Bit SPI VOUT DACs with 10ppm/°C Reference 标准包装:91 系列:- 设置时间:4µs 位数:10 数据接口:MICROWIRE?,串行,SPI? 转换器数目:8 电压电源:单电源 功率耗散(最大):2.7mW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-WFDFN 裸露焊盘 供应商设备封装:14-DFN-EP(4x3) 包装:管件 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD8803 | 制造商:AD 制造商全称:Analog Devices 功能描述:Octal 8-Bit TrimDAC with Power Shutdown |

| AD8803AN | 制造商:Rochester Electronics LLC 功能描述:8CH 8-BIT TDAC W/VREFL SHDN - Bulk |

| AD8803AR | 功能描述:IC DAC 8BIT OCTAL W/SD 16-SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TrimDAC® 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

| AD8803AR-REEL | 制造商:Analog Devices 功能描述:DAC 8-CH R-2R 8-bit 16-Pin SOIC N T/R 制造商:Rochester Electronics LLC 功能描述:8CH 8-BIT TRIMDAC W/PWR SHDN - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。