- 您现在的位置:买卖IC网 > PDF目录373960 > AD9224ARS (ANALOG DEVICES INC) Complete 12-Bit 40 MSPS Monolithic A/D Converter PDF资料下载

参数资料

| 型号: | AD9224ARS |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | ADC |

| 英文描述: | Complete 12-Bit 40 MSPS Monolithic A/D Converter |

| 中文描述: | 1-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| 封装: | SSOP-28 |

| 文件页数: | 11/24页 |

| 文件大小: | 309K |

| 代理商: | AD9224ARS |

AD9224

–11–

REV. A

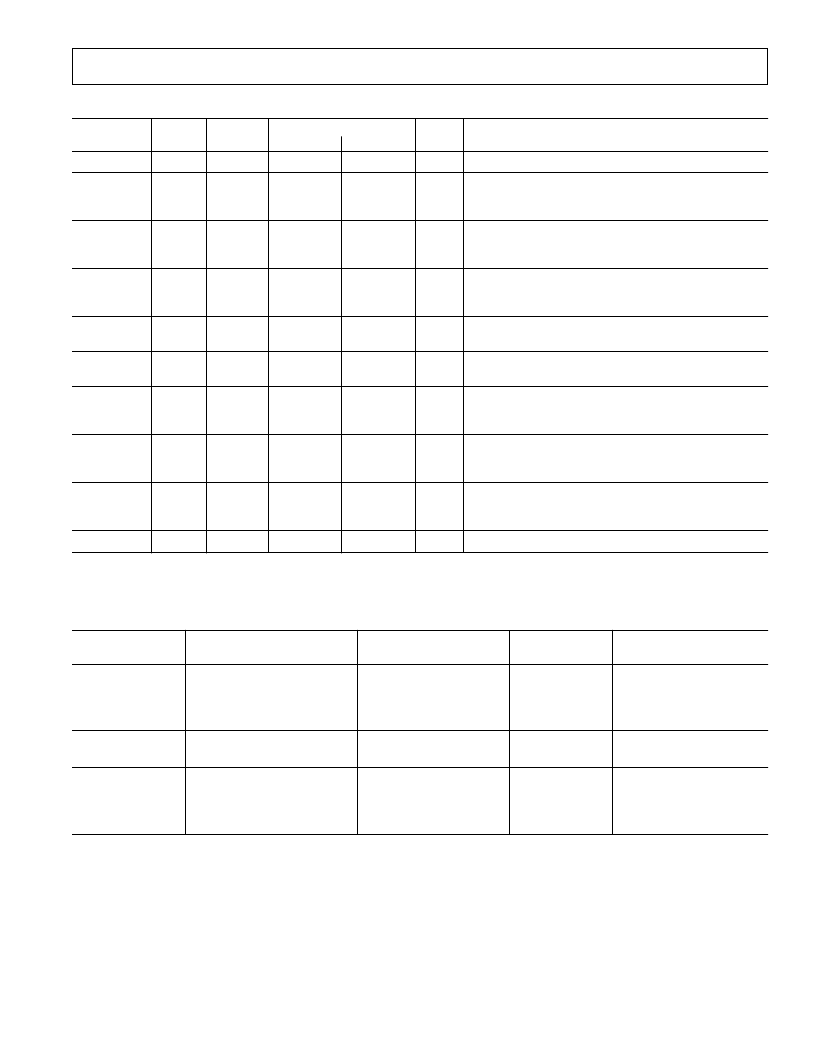

Table I. Analog Input Configuration Summary

Input

Connection

Input

Span (V)

Input Range (V)

VINA

1

Figure

#

Coupling

VINB

1

Comments

Single-Ended

DC

2

0 to 2

1

19, 20

Best for stepped input response applications, requires

±

5 V op amp.

2

×

VREF

0 to

2

×

VREF

VREF

19, 20

Same as above but with improved noise performance due to

increase in dynamic range. Headroom/settling time require-

ments of

±

5 op amp should be evaluated.

4

0 to 4

2.0

19, 20

Optimum noise performance, excellent SNR performance, often

requires low distortion op amp with VCC > +5 V due to its head-

room issues.

2

×

VREF

2.0 – VREF

to

2.0 + VREF

2.0

30

Optimum THD performance with VREF = 1. Single supply

operation (i.e., +5 V) for many op amps.

Single-Ended

AC

2 or

2

×

VREF

0 to 1 or

0 to 2

×

VREF

1 or VREF

21, 22

4

0.5 to 4.5

2.5

22

Optimum noise performance, excellent THD performance,

ability to use

±

5 V op amp.

2

×

VREF

2.0 – VREF

to

2.0 + VREF

2.0

21

Flexible input range, Optimum THD performance with

VREF = 1. Ability to use either +5 V or

±

5 V op amp.

Differential

(via Transformer)

or Amplifier

AC/DC

2

2 to 3

3 to 2

23, 24

Optimum full-scale THD and SFDR performance well beyond

the A/Ds Nyquist frequency. Preferred mode for undersampling

applications.

2

×

VREF

2.0 – VREF/2

to

2.0 + VREF/2

2.0 + VREF/2

to

2.0 – VREF/2

23, 24

Same as above with the exception that full-scale THD and SFDR

performance can be traded off for better noise performance.

4.0

1.5 to 3.5

3.5 to 1.5

23, 24

Optimum noise performance.

NOTE

1

VINA and VINB can be interchanged if signal inversion is required.

Table II. Reference Configuration Summary

Reference

Operating Mode

INTERNAL

INTERNAL

INTERNAL

Input Span (VINA–VINB)

(V p-p)

2

4

2

≤

SPAN

≤

4 AND

SPAN = 2

×

VREF

Required VREF (V)

1

2

1

≤

VREF

≤

2.0 AND

VREF = (1 + R1/R2)

Connect

SENSE

SENSE

R1

R2

To

VREF

REFCOM

VREF AND SENSE

SENSE AND REFCOM

EXTERNAL

(NONDYNAMIC)

2

≤

SPAN

≤

4

1

≤

VREF

≤

2.0

SENSE

VREF

AVDD

EXT. REF.

EXTERNAL

(DYNAMIC)

2

≤

SPAN

≤

4

CAPT and CAPB

Externally Driven

SENSE

VREF

EXT. REF.

EXT. REF.

AVDD

AVSS

CAPT

CAPB

相关PDF资料 |

PDF描述 |

|---|---|

| AD9224 | Complete 12-Bit 40 MSPS Monolithic A/D Converter |

| AD9224-EB | Complete 12-Bit 40 MSPS Monolithic A/D Converter |

| AD9225 | Complete 12-Bit, 25 MSPS Monolithic A/D Converter |

| AD9225-EB | Complete 12-Bit, 25 MSPS Monolithic A/D Converter |

| AD9225AR | Complete 12-Bit, 25 MSPS Monolithic A/D Converter |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9224ARSZ | 功能描述:IC ADC 12BIT 40MSPS 28-SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6 |

| AD9224ARSZRL | 功能描述:IC ADC 12BIT 40MSPS 28SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD9224-EB | 制造商:Analog Devices 功能描述:Evaluation Kit For Complete 12-Bit, 40 MSPS Monolithic A/D Converter 制造商:Analog Devices 功能描述:EVAL KIT FOR COMPLETE 12-BIT, 40 MSPS MONOLITHIC A/D CNVRTR - Bulk 制造商:Rochester Electronics LLC 功能描述:12-BIT 40 MSPS MONOLITHIC A/D CONVERTER - Bulk |

| AD9224JR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 12-Bit |

| AD9224JRS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 12-Bit |

发布紧急采购,3分钟左右您将得到回复。