- 您现在的位置:买卖IC网 > PDF目录10661 > AD9225ARZ (Analog Devices Inc)IC ADC 12BIT 25MSPS 28-SOIC PDF资料下载

参数资料

| 型号: | AD9225ARZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/25页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT 25MSPS 28-SOIC |

| 标准包装: | 27 |

| 位数: | 12 |

| 采样率(每秒): | 25M |

| 数据接口: | 并联 |

| 转换器数目: | 7 |

| 功率耗散(最大): | 373mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 管件 |

| 输入数目和类型: | 2 个单端,双极;1 个差分,单极 |

| 产品目录页面: | 780 (CN2011-ZH PDF) |

AD9225

–17–

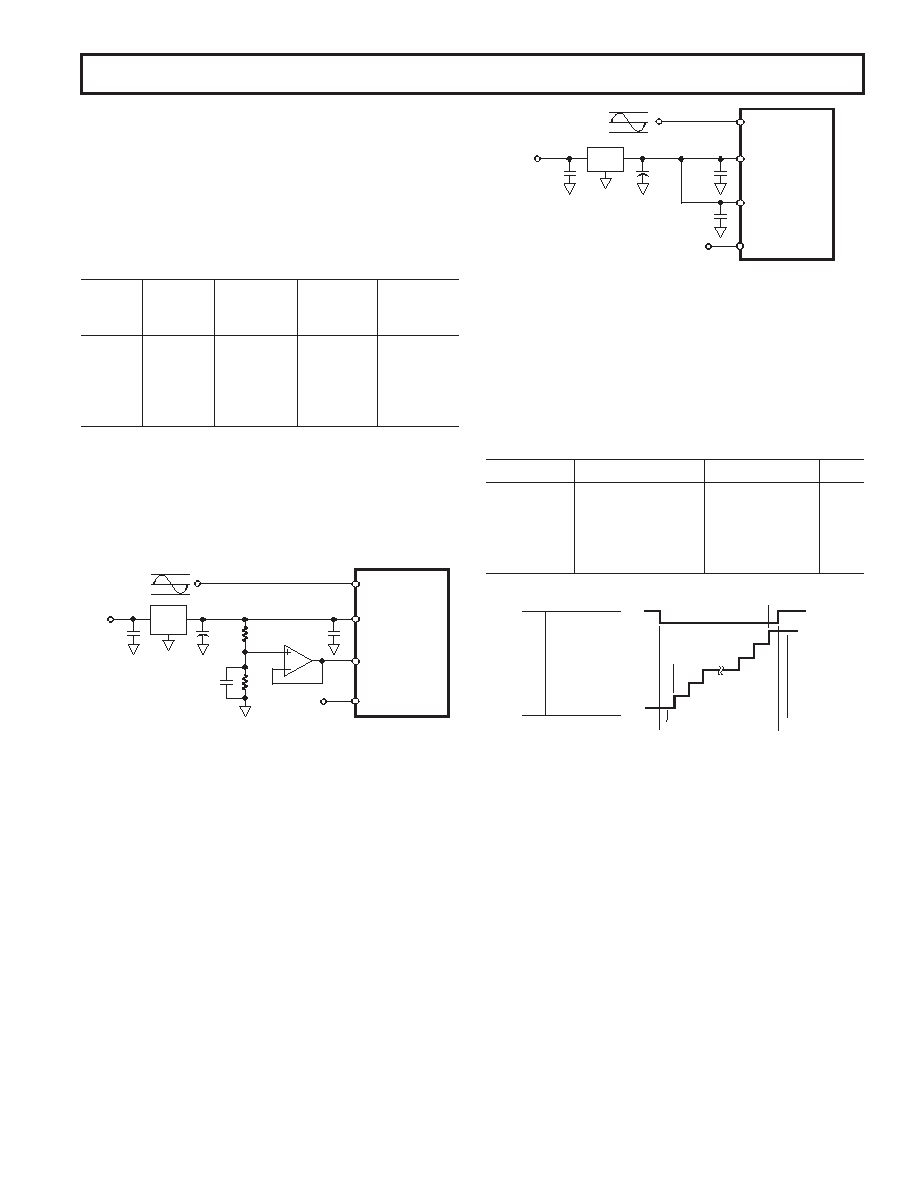

USING AN EXTERNAL REFERENCE

Using an external reference may enhance the dc performance

of the AD9225 by improving drift and accuracy. Figures 20 and 21

show examples of how to use an external reference with the ADC.

Table III is a list of suitable voltage references from Analog

Devices. To use an external reference, the user must disable the

internal reference amplifier and drive the VREF pin. Connecting

the SENSE pin to AVDD disables the internal reference amplifier.

Table III. Suitable Voltage References

Initial

Output

Drift

Accuracy

Operating

Voltage

(ppm/

∞C)

% (max)

Current

Internal

1.00

26

1.4

1 mA

AD589

1.235

10–100

1.2–2.8

50

mA

AD1580

1.225

50–100

0.08–0.8

50

mA

REF191

2.048

5–25

0.1–0.5

45

mA

Internal

2.0

26

1.4

1 mA

The AD9225 contains an internal reference buffer, A2 (see

Figure 5), that simplifies the drive requirements of an external

reference. The external reference must be able to drive about 5

k

W (±20%) load. Note that the bandwidth of the reference

buffer is deliberately left small to minimize the reference noise

contribution. As a result, it is not possible to change the refer-

ence voltage rapidly in this mode.

2.5V+VREF

2.5V–VREF

2.5V

+5V

0.1 F

22 F

VINA

VINB

VREF

SENSE

AD9225

+5V

R2

0.1 F

A1

R1

0.1 F

2.5V

REF

Figure 20. External Reference

Variable Input Span with VCM = 2.5 V

Figure 20 shows an example of the AD9225 configured for an

input span of 2

VREF centered at 2.5 V. An external 2.5 V refer-

ence drives the VINB pin thus setting the common-mode voltage

at 2.5 V. The input span can be independently set by a voltage

divider consisting of R1 and R2, which generates the VREF signal.

A1 buffers this resistor network and drives VREF. Choose this op

amp based on accuracy requirements. It is essential that a mini-

mum of a 10

mF capacitor in parallel with a 0.1 mF low inductance

ceramic capacitor decouple A1’s output to ground.

Single-Ended Input with 0 to 2

VREF Range

Figure 21 shows an example of an external reference driving both

VINB and VREF. In this case, both the common-mode voltage

and input span are directly dependent on the value of VREF. More

specifically, the common-mode voltage is equal to VREF while the

input span is equal to 2

VREF. The valid input range extends

from 0 to 2

VREF. For example, if the REF191, a 2.048 V exter-

nal reference was selected, the valid input range extends from 0 to

4.096 V. In this case, 1 LSB of the AD9225 corresponds to 1 mV.

It is essential that a minimum of a 10

mF capacitor in parallel with a

0.1

mF low inductance ceramic capacitor decouple the reference

output to ground.

2

REF

0V

+5V

10 F

VINA

VINB

VREF

SENSE

AD9225

+5V

0.1 F

VREF

0.1 F

Figure 21. Input Range = 0 V to 2

VREF

DIGITAL INPUTS AND OUTPUTS

Digital Outputs

The AD9225 output data is presented in positive true straight

binary for all input ranges. Table IV indicates the output data

formats for various input ranges regardless of the selected input

range. A twos complement output data format can be created by

inverting the MSB.

Table IV. Output Data Format

Input (V)

Condition (V)

Digital Output

OTR

VINA–VINB

< – VREF

0000 0000 0000

1

VINA–VINB

= – VREF

0000 0000 0000

0

VINA–VINB

= 0

1000 0000 0000

0

VINA–VINB

= + VREF – 1 LSB

1111 1111 1111

0

VINA–VINB

≥ + VREF

1111 1111 1111

1

1111 1111 1111

1111 1111 1110

OTR

–FS

+FS

–FS+1/2 LSB

+FS –1/2 LSB

–FS –1/2 LSB

+FS –1 1/2 LSB

0000 0000 0001

0000 0000 0000

1

0

1

OTR DATA OUTPUTS

Figure 22. Output Data Format

Out-Of-Range (OTR)

An out-of-range condition exists when the analog input voltage is

beyond the input range of the converter. OTR is a digital output

that is updated along with the data output corresponding to the

particular sampled analog input voltage. OTR has the same pipe-

line delay (latency) as the digital data. It is low when the analog

input voltage is within the analog input range. It is high when the

analog input voltage exceeds the input range as shown in Figure

23. OTR will remain high until the analog input returns within

the input range and another conversion is completed. By logical

ANDing OTR with the MSB and its complement, overrange high

or underrange low conditions can be detected. Table V is a truth

table for the overrange circuit in Figure 24 which uses NAND

gates. Systems requiring programmable gain conditioning of the

AD9225 input signal can immediately detect an out-of-range

condition, eliminating gain selection iterations. OTR can also be

used for digital offset and gain calibration.

Rev. C

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B1W-IV-F2 | CONVERTER MOD DC/DC 5.5V 150W |

| MAX13430EETB+T | TXRX RS-485 0.5MBPS HALF 10TDFN |

| LTC2247CUH#PBF | IC ADC 14BIT 40MSPS SAMPL 32-QFN |

| MAX9203ESA+T | IC COMPARATOR LP 8-SOIC |

| VE-B1W-IV-F1 | CONVERTER MOD DC/DC 5.5V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9225ARZRL | 功能描述:IC ADC 12BIT 25MSPS 28SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD9225-EB | 制造商:Analog Devices 功能描述: 制造商:Analog Devices 功能描述:DEV TOOLS, EVAL BD FOR AD9225 - Bulk |

| AD9226 | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 12-Bit, 65 MSPS ADC Converter |

| AD9226_01 | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 12-Bit, 65 MSPS ADC Converter |

| AD9226ARS | 功能描述:IC ADC 12BIT 65MSPS 28-SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:12 采样率(每秒):3M 数据接口:- 转换器数目:- 功率耗散(最大):- 电压电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:SOT-23-6 供应商设备封装:SOT-23-6 包装:带卷 (TR) 输入数目和类型:- |

发布紧急采购,3分钟左右您将得到回复。