- 您现在的位置:买卖IC网 > PDF目录1893 > AD9393BBCZRL-80 (Analog Devices Inc)IC INTERFACE 80MHZ HDMI 76CSPBGA PDF资料下载

参数资料

| 型号: | AD9393BBCZRL-80 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 37/40页 |

| 文件大小: | 0K |

| 描述: | IC INTERFACE 80MHZ HDMI 76CSPBGA |

| 标准包装: | 2,500 |

| 应用: | HDMI,DVI,接收器 |

| 接口: | 模拟,DVI |

| 电源电压: | 3.15 V ~ 3.47 V |

| 封装/外壳: | 76-LFBGA,CSPBGA |

| 供应商设备封装: | 76-CSPBGA(6x6) |

| 包装: | 带卷 (TR) |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页

AD9393

Rev. 0 | Page 6 of 40

AD9393

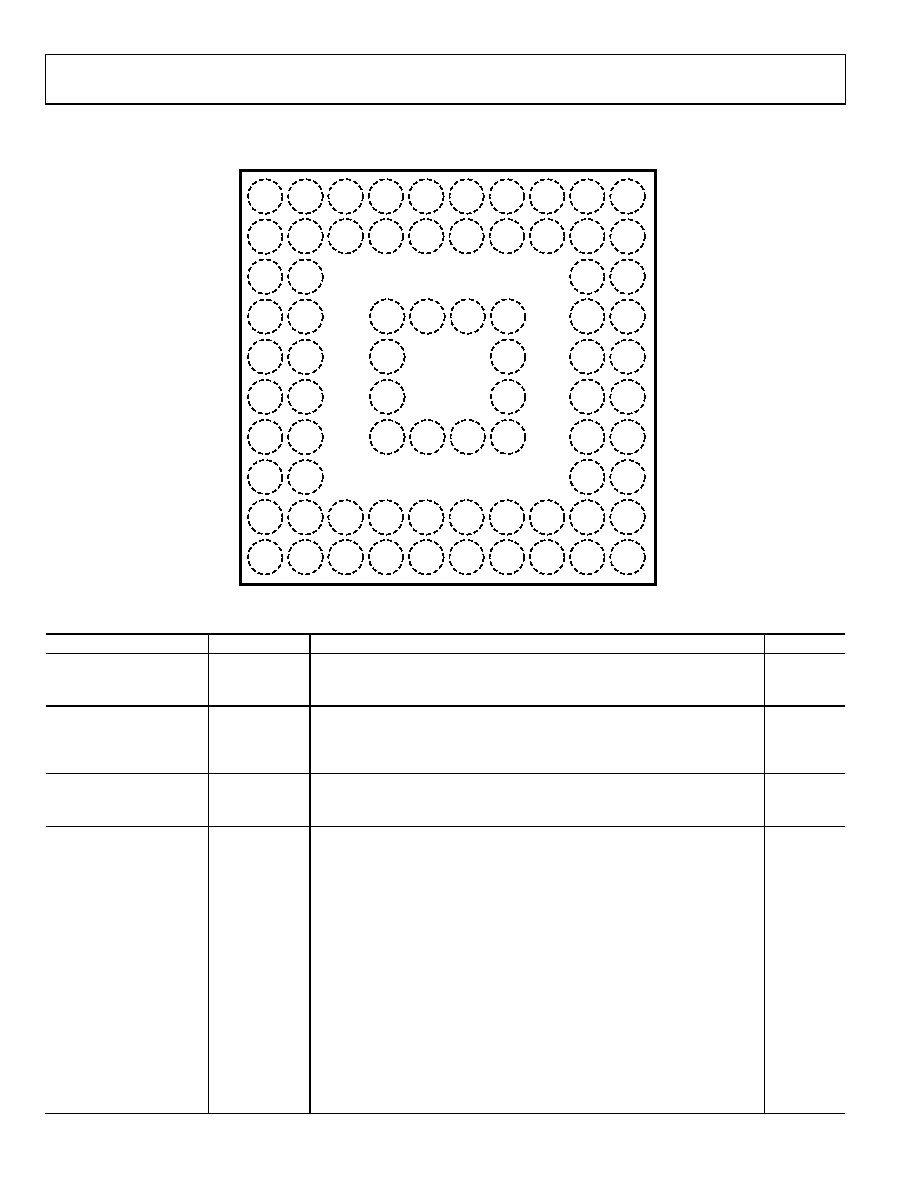

TOP VIEW

(Not to Scale)

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

D14

D15

D16

D18

D20

D22

DCLK

HSOUT

O/E

SDA

D13

D12

D17

D19

D21

D23

DE

VDD

GND

VD

GND

VD

SCLK

LRCLK

DVDD

VSOUT

PD

SCL

GND

MCLK

I2S3

I2S2

I2S1

I2S0

SPDIF

RTERM

DDC_

SDA

Rx2+

RxC–

RxC+

GND

Rx0–

Rx0+

GND

Rx1–

Rx1+

GND

Rx2–

D11

D10

GND

D9

D8

GND

FILT

D7

D6

GND

D5

D4

PVDD

MDA

D3

D2

PVDD

MCL

D1

D0

DDC_

SCL

GND

A

123

456

789

10

B

J

K

C

D

E

F

G

H

08

04

3-

0

02

Figure 2. Pin Configuration

Table 4. Complete Pin List

Pin No.

Mnemonic

Description

Value

Inputs

B9

PD

Power-Down Control. Power-Down Control/Three-State Control. The function

of this pin is programmable via Register 0x26[2:1].

3.3 V CMOS

Digital Video Data Inputs

K5, K4, K8, K7, J10, K10

Rx0+, Rx0,

Rx1+, Rx1,

Rx2+, Rx2

Digital Input Channel x True/Complement. These six pins receive three pairs of

transition minimized differential signaling (TMDS ) pixel data (at 10× the pixel

rate) from a digital graphics transmitter.

TMDS

Digital Video Clock Inputs

K2, K1

RxC+, RxC

Digital Data Clock True/Complement. This clock pair receives a TMDS clock at

1× pixel data rate.

TMDS

Outputs

B6, A6, B5, A5, B4,

A4, B3, A3, A2, A1,

B1, B2, C1, C2, D1,

D2, E1, E2, F1, F2,

G1, G2, H1, H2

D[23:0]

Data Outputs. In RGB,

D[23:16] = Red[7:0]

D[15:8] = Green[7:0]

D[7:0] = Blue[7:0]

See Table 6

VDD

A7

DCLK

Data Output Clock. This is the main clock output signal used to strobe the

output data and HSOUT into external logic. Four possible output clocks can

be selected with Register 0x25[7:6]. These are related to the pixel clock (×

pixel clock, 1× pixel clock, 2× frequency pixel clock, and a 90° phase shifted

pixel clock). They are produced by the internal PLL clock generator and are

synchronous with the pixel clock. The polarity of DCLK can also be inverted via

Register 0x24[0].

VDD

A8

HSOUT

HSYNC Output Clock (Phase-Aligned with DCLK). Horizontal sync output. A

reconstructed and phase-aligned version of the HSYNC input. Both the

polarity and duration of this output can be programmed via serial bus

registers. By maintaining alignment with DCLK and data, data timing with

respect to horizontal sync can always be determined.

VDD

相关PDF资料 |

PDF描述 |

|---|---|

| AD9398KSTZ-150 | IC INTERFACE 150MHZ HDMI 100LQFP |

| AD9708ARU | IC DAC 8BIT 100MSPS 28-TSSOP |

| AD974BN | IC DAS 16BIT 4CH 200KSPS 28-DIP |

| AD9755ASTZRL | IC DAC 14BIT 300MSPS 48-LQFP |

| AD9762ARU | IC DAC 12BIT 125MSPS 28-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9394BCBZ-R7 | 功能描述:IC INTERFACE HDMI 12WLCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 电源管理 - 专用 系列:- 标准包装:1 系列:- 应用:手持/移动设备 电流 - 电源:- 电源电压:3 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-WFDFN 裸露焊盘 供应商设备封装:14-LLP-EP(4x4) 包装:Digi-Reel® 配用:LP3905SD-30EV-ND - BOARD EVALUATION LP3905SD-30 其它名称:LP3905SD-30DKR |

| AD9396 | 制造商:AD 制造商全称:Analog Devices 功能描述:Analog/DVI Dual-Display Interface |

| AD9396/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Analog/DVI Dual-Display Interface |

| AD9396KSTZ-100 | 制造商:Analog Devices 功能描述:Analog/DVI Dual Display Interface 100-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD9396KSTZ-150 | 制造商:AD 制造商全称:Analog Devices 功能描述:Analog/DVI Dual-Display Interface |

发布紧急采购,3分钟左右您将得到回复。