参数资料

| 型号: | AD9520-5BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 51/76页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN EXT VCO 64-LFCSP |

| 设计资源: | Synchronizing Multiple AD9910 1 GSPS Direct Digital Synthesizers (CN0121) Phase Coherent FSK Modulator (CN0186) |

| 标准包装: | 1 |

| 类型: | 时钟发生器,扇出配送 |

| PLL: | 是 |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:12,2:24 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.4GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 产品目录页面: | 776 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

Data Sheet

AD9520-5

Rev. A | Page 55 of 76

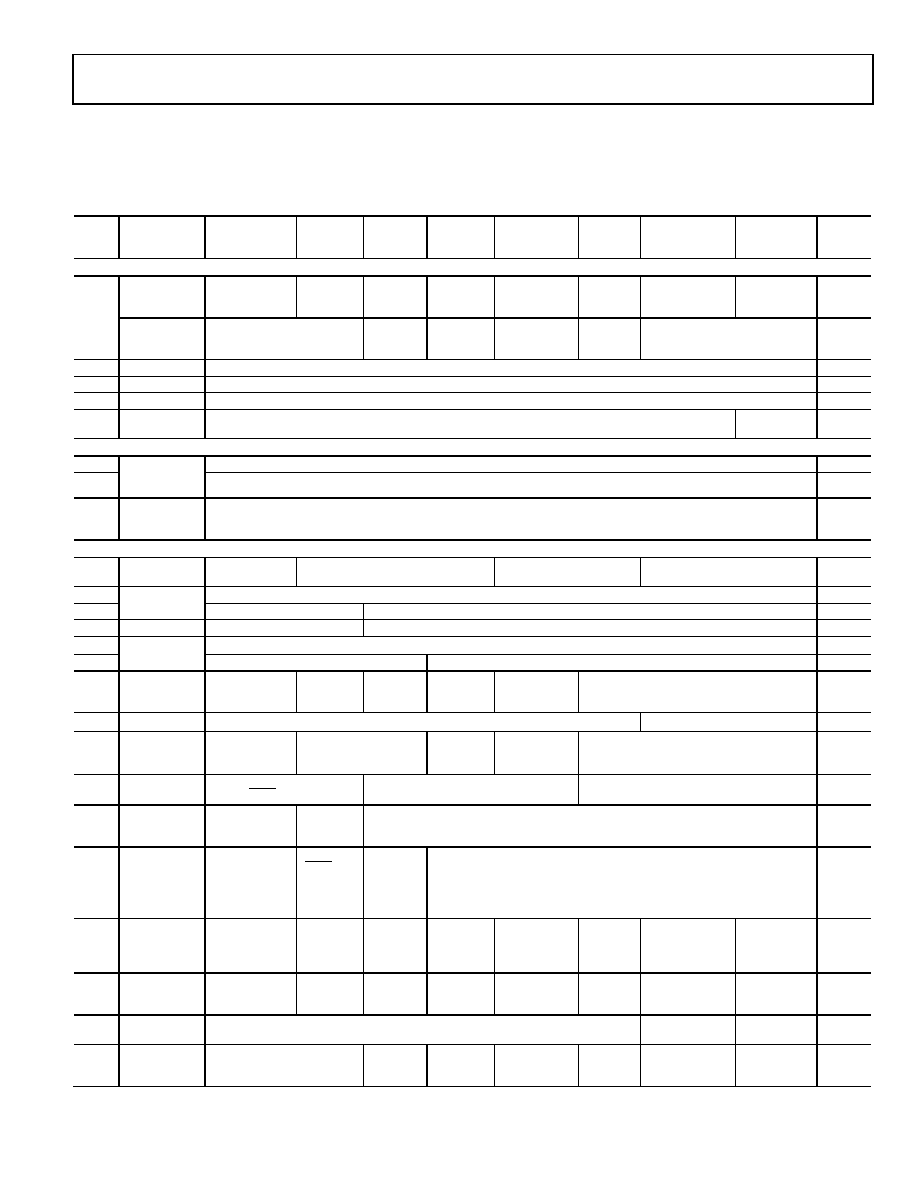

REGISTER MAP

Register addresses that are not listed in Table 44 are not used, and writing to those registers has no effect. Writing to register addresses

that are marked as unused also has no effect.

Table 44. Register Map Overview

Addr.

(Hex)

Parameter

Bit 7 (MSB)

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0 (LSB)

Default

Value

(Hex)

Serial Port Configuration

0x000

Serial port

config

(SPI mode)

SDO active

LSB first/

addr incr

Soft reset

(self-clear)

Unused

Soft reset

(self-clear)

LSB first/addr incr

SDO active

0x00

Serial port

config

(IC mode)

Unused

Soft reset

(self-clear)

Unused

Soft reset

(self-clear)

Unused

0x00

0x001

Unused

N/A

0x002

Reserved

N/A

0x003

Part ID

Part ID (read only)

0x20

0x004

Readback

control

Unused

Read back

active regs

0x00

EEPROM ID

0x005

EEPROM

customer

version ID

EEPROM customer version ID (LSB)

0x00

0x006

EEPROM customer version ID (MSB)

0x00

0x007

to

0x00F

Unused

0x00

PLL

0x010

PFD charge

pump

PFD polarity

Charge pump current

Charge pump mode

PLL power-down

0x7D

0x011

R counter

14-bit R counter, Bits[7:0] (LSB)

0x01

0x012

Unused

14-bit R counter, Bits[13:8] (MSB)

0x00

0x013

A counter

Unused

6-bit A counter

0x00

0x014

B counter

13-bit B counter, Bits[7:0] (LSB)

0x03

0x015

Unused

13-bit B counter, Bits[12:8] (MSB)

0x00

0x016

PLL_CTRL_1

Set CP pin

to VCP/2

Reset

R counter

Reset

A and B

counters

Reset all

counters

B counter

bypass

Prescaler P

0x06

0x017

PLL_CTRL_2

STATUS pin control

Antibacklash pulse width

0x00

0x018

PLL_CTRL_3

Enable CMOS

reference input

dc offset

Lock detect counter

Digital lock

detect

window

Disable digital

lock detect

Unused

0x06

0x019

PLL_CTRL_4

R, A, and B counters

SYNC pin reset

R path delay

N path delay

0x00

0x01A

PLL_CTRL_5

Enable

STATUS pin

divider

Ref freq

monitor

threshold

LD pin control

0x00

0x01B

PLL_CTRL_6

Enable CLK

frequency

monitor

Enable REF2

(REFIN)

frequency

monitor

Enable

REF1

(REFIN)

frequency

monitor

REFMON pin control

0x00

0x01C

PLL_CTRL_7

Disable

switchover

deglitch

Select REF2

Use

REF_SEL

pin

Enable

automatic

reference

switchover

Stay on REF2

Enable

REF2

Enable

REF1

Enable

differential

reference

0x00

0x01D

PLL_CTRL_8

Enable

STATUS_EEPROM

at STATUS pin

Enable

XTAL OSC

Enable

clock

doubler

Disable

PLL status

register

Enable LD pin

comparator

Unused

Enable

external holdover

Enable

holdover

0x80

0x01E

PLL_CTRL_9

Unused

Enable

zero delay

Unused

0x00

0x01F

PLL_Readback

(read only)

Unused

Holdover

active

REF2

selected

CLK

freq > threshold

REF2

freq >

threshold

REF1 freq >

threshold

Digital lock

detect

N/A

相关PDF资料 |

PDF描述 |

|---|---|

| M83723/83G1203N | CONN RCPT 3POS WALL MT W/PINS |

| X9116WM8 | IC DIGITAL POT 10K 16TP 8MSOP |

| MS27467E25F35SD | CONN PLUG 128POS STRAIGHT W/SCKT |

| X9111TV14I | IC DCP 100K 1024TP 14TSSOP |

| MS3452W28-2S | CONN RCPT 14POS BOX MNT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9520-5BCPZ-REEL7 | 功能描述:IC CLOCK GEN EXT VCO 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| AD9521JH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Log/Antilog Amplifier |

| AD9521KH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Log/Antilog Amplifier |

| AD9521SE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Log/Antilog Amplifier |

| AD9521SH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Log/Antilog Amplifier |

发布紧急采购,3分钟左右您将得到回复。