- 您现在的位置:买卖IC网 > PDF目录1987 > AD9557BCPZ-REEL7 (Analog Devices Inc)IC CLK XLATR PLL 1250MHZ 40LFCSP PDF资料下载

参数资料

| 型号: | AD9557BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/92页 |

| 文件大小: | 0K |

| 描述: | IC CLK XLATR PLL 1250MHZ 40LFCSP |

| 产品变化通告: | Minor Mask Change 11/Apr/2012 |

| 标准包装: | 750 |

| 类型: | 时钟/频率转换器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,HSTL,LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.25GHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

Data Sheet

AD9557

Rev. B | Page 13 of 92

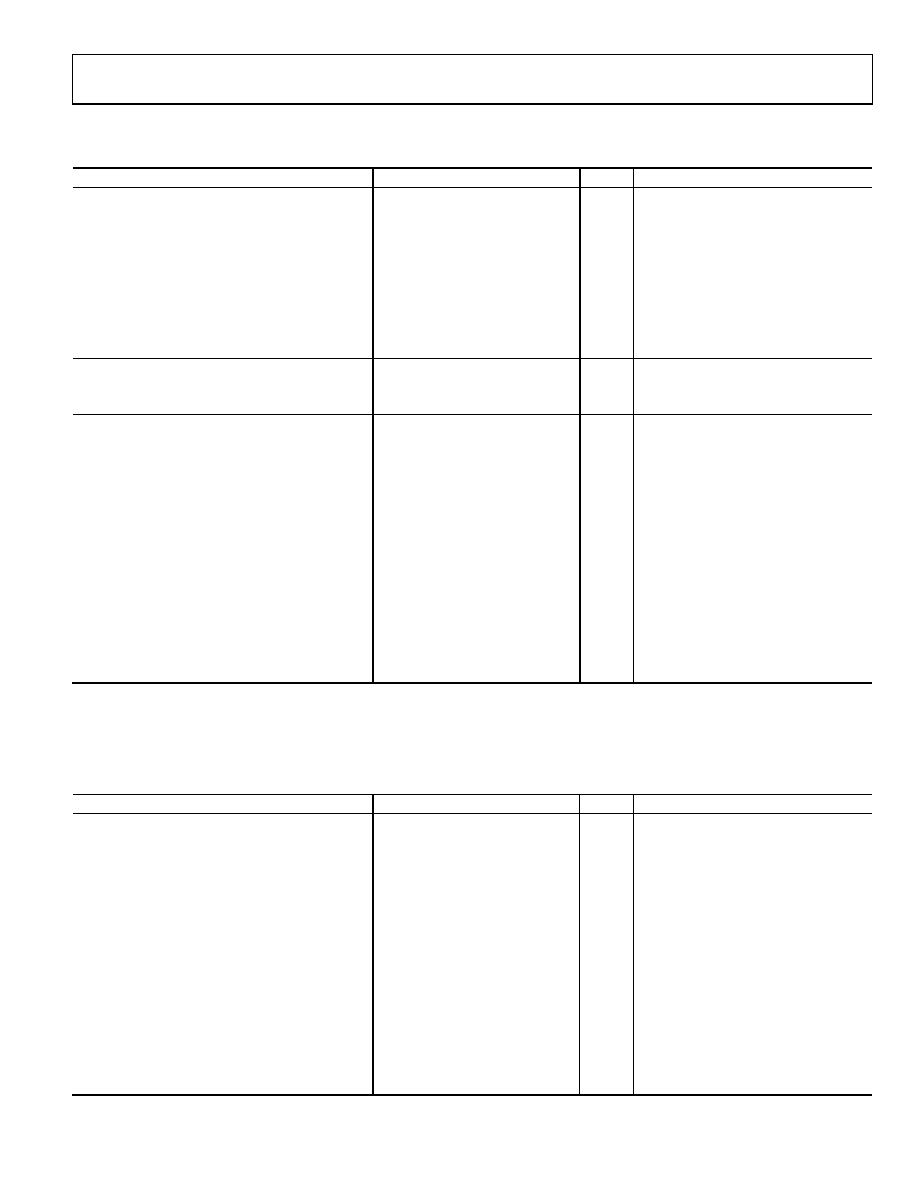

SERIAL PORT SPECIFICATIONS—I2C MODE

Table 16.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

SDA, SCL (AS INPUT)

Input Logic 1 Voltage

0.7 ×

DVDD3

V

Input Logic 0 Voltage

0.3 ×

DVDD3

V

Input Current

10

+10

A

For VIN = 10% to 90% DVDD3

Hysteresis of Schmitt Trigger Inputs

0.015 ×

DVDD3

Pulse Width of Spikes That Must Be Suppressed

by the Input Filter, tSP

50

ns

SDA (AS OUTPUT)

Output Logic 0 Voltage

0.4

V

IO = 3 mA

Output Fall Time from VIHmin to VILmax

20 + 0.1 Cb

250

ns

TIMING

SCL Clock Rate

400

kHz

Bus-Free Time Between a Stop and Start Condition,

tBUF

1.3

s

Repeated Start Condition Setup Time, tSU; STA

0.6

s

Repeated Hold Time Start Condition, tHD;STA

0.6

s

After this period, the first clock pulse

is generated

Stop Condition Setup Time, tSU; STO

0.6

s

Low Period of the SCL Clock, tLOW

1.3

s

High Period of the SCL Clock, tHIGH

0.6

s

SCL/SDA Rise Time, tR

20 + 0.1 Cb1

300

ns

SCL/SDA Fall Time, tF

20 + 0.1 Cb1

300

ns

Data Setup Time, tSU; DAT

100

ns

Data Hold Time, tHD; DAT

100

ns

Capacitive Load for Each Bus Line, Cb1

400

pF

1

Cb is the capacitance (pF) of a single bus line.

JITTER GENERATION

Jitter generation (random jitter) uses 49.152 MHz crystal for system clock input.

Table 17.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

JITTER GENERATION

System clock doubler enabled;

high phase margin mode enabled;

Register 0x0405 = 0x20; Register 0x0403 =

0x07; Register 0x0400 = 0x81; in cases

where multiple driver types are listed,

both driver types were tested at those

conditions, and the one with higher jitter

is quoted, although there is usually not

a significant jitter difference between

the driver types

fREF = 19.44 MHz; fOUT = 622.08 MHz; fLOOP = 50 Hz

HSTL Driver

Bandwidth: 5 kHz to 20 MHz

304

fs rms

Bandwidth: 12 kHz to 20 MHz

296

fs rms

Bandwidth: 20 kHz to 80 MHz

300

fs rms

Bandwidth: 50 kHz to 80 MHz

266

fs rms

Bandwidth: 16 MHz to 320 MHz

185

fs rms

相关PDF资料 |

PDF描述 |

|---|---|

| AD9558BCPZ-REEL7 | IC CLK XLATR PLL 1250MHZ 64LFCSP |

| AD9571ACPZPEC-R7 | IC PLL CLOCK GEN 25MHZ 40LFCSP |

| AD9572ACPZLVD-R7 | IC PLL CLOCK GEN 25MHZ 40LFCSP |

| AD9573ARUZ-RL7 | IC PCI CLCOK GEN 25MHZ 16TSSOP |

| AD9575ARUZPEC | IC PLL CLOCK GEN 25MHZ 16TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9558 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad Input Multiservice Line Card Adaptive |

| AD9558/PCBZ | 功能描述:BOARD EVAL FOR AD9558 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| AD9558BCPZ | 功能描述:IC CLOCK TRANSLATOR 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| AD9558BCPZ-REEL7 | 功能描述:IC CLK XLATR PLL 1250MHZ 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| AD9559 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual PLL, Quad Input, Multiservice Line Card Adaptive Clock Translator |

发布紧急采购,3分钟左右您将得到回复。