- 您现在的位置:买卖IC网 > PDF目录17021 > AD9653-125EBZ (Analog Devices Inc)BOARD EVAL FOR AD9653 PDF资料下载

参数资料

| 型号: | AD9653-125EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/40页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9653 |

| 标准包装: | 1 |

| ADC 的数量: | 4 |

| 位数: | 16 |

| 采样率(每秒): | 125M |

| 数据接口: | LVDS,串行,SPI? |

| 输入范围: | 2 Vpp |

| 在以下条件下的电源(标准): | 673mW @ 125MSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD9653 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

AD9653

Data Sheet

Rev. 0 | Page 22 of 40

THEORY OF OPERATION

The AD9653 is a multistage, pipelined ADC. Each stage

provides sufficient overlap to correct for flash errors in the

preceding stage. The quantized outputs from each stage are

combined into a final 16-bit result in the digital correction

logic. The serializer transmits this converted data in a 16-bit

output. The pipelined architecture permits the first stage to

operate with a new input sample while the remaining stages

operate with preceding samples. Sampling occurs on the rising

edge of the clock.

Each stage of the pipeline, excluding the last, consists of a low

resolution flash ADC connected to a switched-capacitor DAC

and an interstage residue amplifier (for example, a multiplying

digital-to-analog converter (MDAC)). The residue amplifier

magnifies the difference between the reconstructed DAC output

and the flash input for the next stage in the pipeline. One bit of

redundancy is used in each stage to facilitate digital correction

of flash errors. The last stage simply consists of a flash ADC.

The output staging block aligns the data, corrects errors, and

passes the data to the output buffers. The data is then serialized

and aligned to the frame and data clocks.

ANALOG INPUT CONSIDERATIONS

The analog input to the AD9653 is a differential switched-

capacitor circuit designed for processing differential input

signals. This circuit can support a wide common-mode range

while maintaining excellent performance. By using an input

common-mode voltage of midsupply, users can minimize

signal-dependent errors and achieve optimum performance.

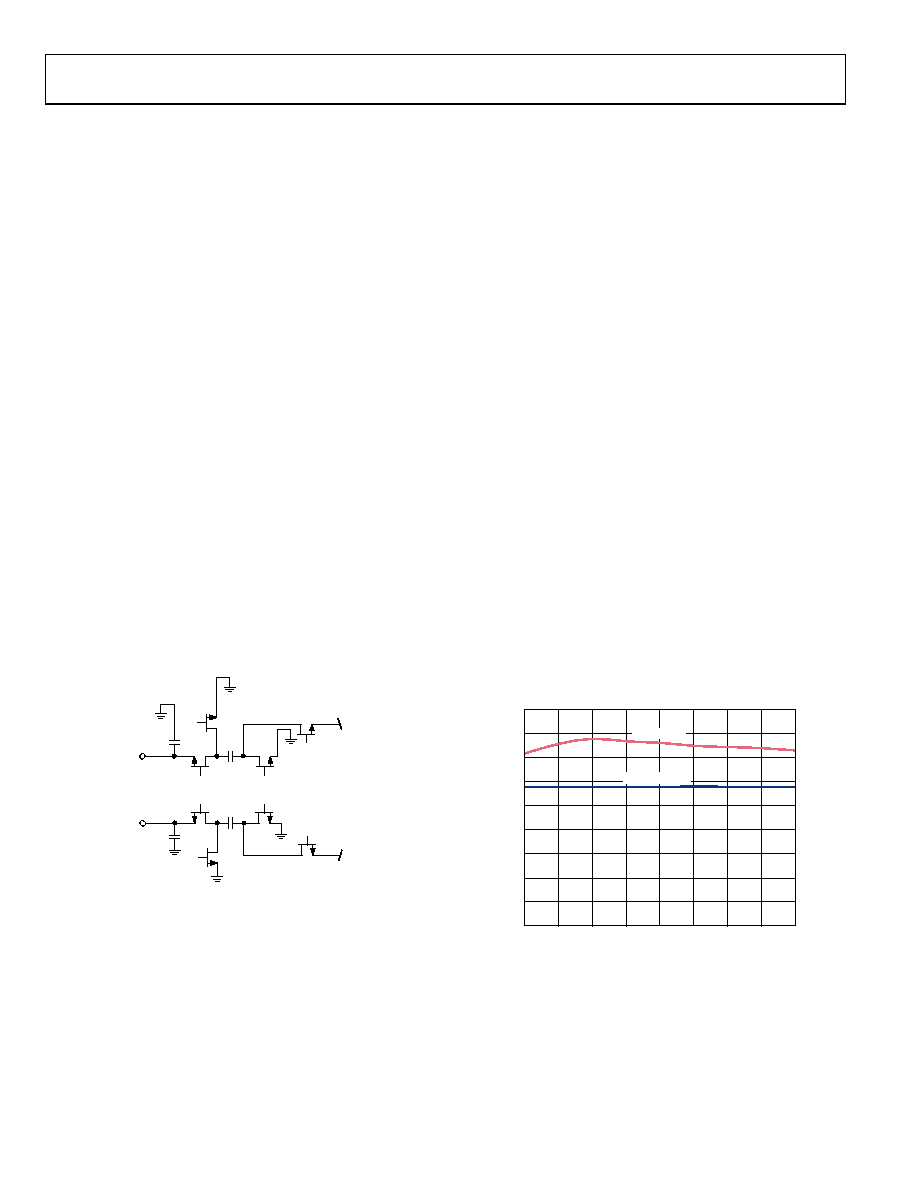

Figure 51. Switched-Capacitor Input Circuit

The clock signal alternately switches the input circuit between

sample mode and hold mode (see Figure 51). When the input

circuit is switched to sample mode, the signal source must be

capable of charging the sample capacitors and settling within

one-half of a clock cycle. A small resistor in series with each

input can help reduce the peak transient current injected from

the output stage of the driving source. In addition, low Q inductors

or ferrite beads can be placed on each leg of the input to reduce

high differential capacitance at the analog inputs and therefore

achieve the maximum bandwidth of the ADC. Such use of low

Q inductors or ferrite beads is required when driving the converter

front end at high IF frequencies. Either a differential capacitor or

two single-ended capacitors can be placed on the inputs to

provide a matching passive network. This ultimately creates a

low-pass filter at the input to limit unwanted broadband noise.

and the Analog Dialogue article “Transformer-Coupled Front-

End for Wideband A/D Converters” (Volume 39, April 2005) for

more information. In general, the precise values depend on the

application.

Input Common Mode

The analog inputs of the AD9653 are not internally dc-biased.

Therefore, in ac-coupled applications, the user must provide

this bias externally. Setting the device so that VCM = AVDD/2 is

recommended for optimum performance, but the device can

function over a wider range with reasonable performance, as

shown in Figure 52 and Figure 53.

An on-chip, common-mode voltage reference is included in the

design and is available from the VCM pin. The VCM pin must

be bypassed to ground by a 0.1 F capacitor, as described in the

Applications Information section.

Maximum SNR performance is achieved by setting the ADC to

the largest span in a differential configuration. In the case of the

AD9653, the input span is dependent on the reference voltage

(see Table 11).

Figure 52. SNR/SFDR vs. Common-Mode Voltage,

fIN = 9.7 MHz, fSAMPLE = 125 MSPS, VREF = 1.0 V

S

H

CPAR

CSAMPLE

CPAR

VIN–x

H

S

H

VIN+x

H

10538-

051

20

30

40

50

60

70

80

90

100

110

0.5

0.6

0.7

0.8

0.9

1.0

1.1

1.2

1.3

S

NR/

S

F

DR

(

d

BF

S

/d

Bc)

COMMON-MODE VOLTAGE (V)

SFDR (dBc)

SNRFS (dBFS)

10538-

052

相关PDF资料 |

PDF描述 |

|---|---|

| CDB5532U | BOARD EVAL FOR CS5532U ADC |

| CDB5530U | BOARD EVAL FOR CS5530 |

| SIP4613ADVP-T1-E3 | IC LOAD SW HISIDE 1A SC75-6 |

| CDB5534U | EVAL BOARD FOR CS5534 |

| AD9648-125EBZ | EVAL BOARD AD9648-125 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9653BCPZ-125 | 制造商:Analog Devices 功能描述:16 BIT 125MSPS 1.8V QUAD ADC - Trays 制造商:Analog Devices 功能描述:IC ADC 16BIT SRL 125MSPS 48LFCSP 制造商:Analog Devices 功能描述:ADC QUAD 16BIT 125MSPS 48LFCSP 制造商:Analog Devices 功能描述:ADC, QUAD, 16BIT, 125MSPS, 48LFCSP 制造商:Analog Devices 功能描述:16 Bit 125Msps 1.8V Quad ADC 制造商:Analog Devices 功能描述:IC, ADC, 16BIT, 125MSPS, SPI, LFCSP-48, Resolution (Bits):16bit, Sampling Rate:125MSPS, Supply Voltage Type:Single, Supply Voltage Min:1.7V, Supply Voltage Max:1.9V, Supply Current:305mA, Digital IC Case Style:LFCSP, No. of Pins:48 , RoHS Compliant: Yes 制造商:Analog Devices 功能描述:CONVERTER - ADC |

| AD9653BCPZRL7-125 | 功能描述:IC ADC 16BIT 125MSPS SRL 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD9655-125EBZ | 功能描述:AD9655 - 16 Bit 125M Samples per Second Analog to Digital Converter (ADC) Evaluation Board 制造商:analog devices inc. 系列:- 零件状态:有效 A/D 转换器数:2 位数:16 采样率(每秒):125M 数据接口:LVDS - 串行,SPI 输入范围:2.8 Vpp 不同条件下的功率(典型值):313mW @ 125MSPS 使用的 IC/零件:AD9655 所含物品:板 标准包装:1 |

| AD9656BCPZ-125 | 制造商:Analog Devices 功能描述:16BIT 125MSPS 1.8V QUAD ADC W/SERIAL OUT - Trays 制造商:Analog Devices 功能描述:IC ADC 16BIT 125MSPS 56LFCSP |

| AD9656EBZ | 制造商:Analog Devices 功能描述:16BIT 125MSPS 1.8V QUAD ADC W/SERIAL OUT - Boxed Product (Development Kits) |

发布紧急采购,3分钟左右您将得到回复。